- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16278 > 73M1866B-KEYCHN (Maxim Integrated Products)BOARD KEYCHAIN INF DANUBE EVM PDF資料下載

參數(shù)資料

| 型號: | 73M1866B-KEYCHN |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 38/88頁 |

| 文件大小: | 0K |

| 描述: | BOARD KEYCHAIN INF DANUBE EVM |

| 產(chǎn)品培訓模塊: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 標準包裝: | 1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

DS_1x66B_001

73M1866B/73M1966B Data Sheet

Rev. 1.6

43

7.5

GPIO Registers

Three user-defined I/O pins are provided in the 32-pin QFN package of the 73M1966B only. The pins are

GPIO7, GPIO6 and GPIO5.

GPIO pins are not available on the 20-pin package of the 73M1966B.

GPIO pins are not available on the 42-pin package of the 73M1866B.

Each pin can be configured independently as either an input or an output by writing to the corresponding

I/O Direction (DIR) register.

At power on and after a reset, the GPIO pins are initialized to a high impedance state to avoid unwanted

current contention and consumption. The input structures are protected from floating inputs, and no

output levels are driven by any of the GPIO pins.

The mapping of GPIO pins is designed to correspond to the bit location in their control and status

registers.

The 73M1x66B supports the ability to generate an interrupt on the

INT pin. The source can be configured

to generate on a rising or a trailing edge. Only GPIO ports that are configured as inputs can be used to

generate interrupts.

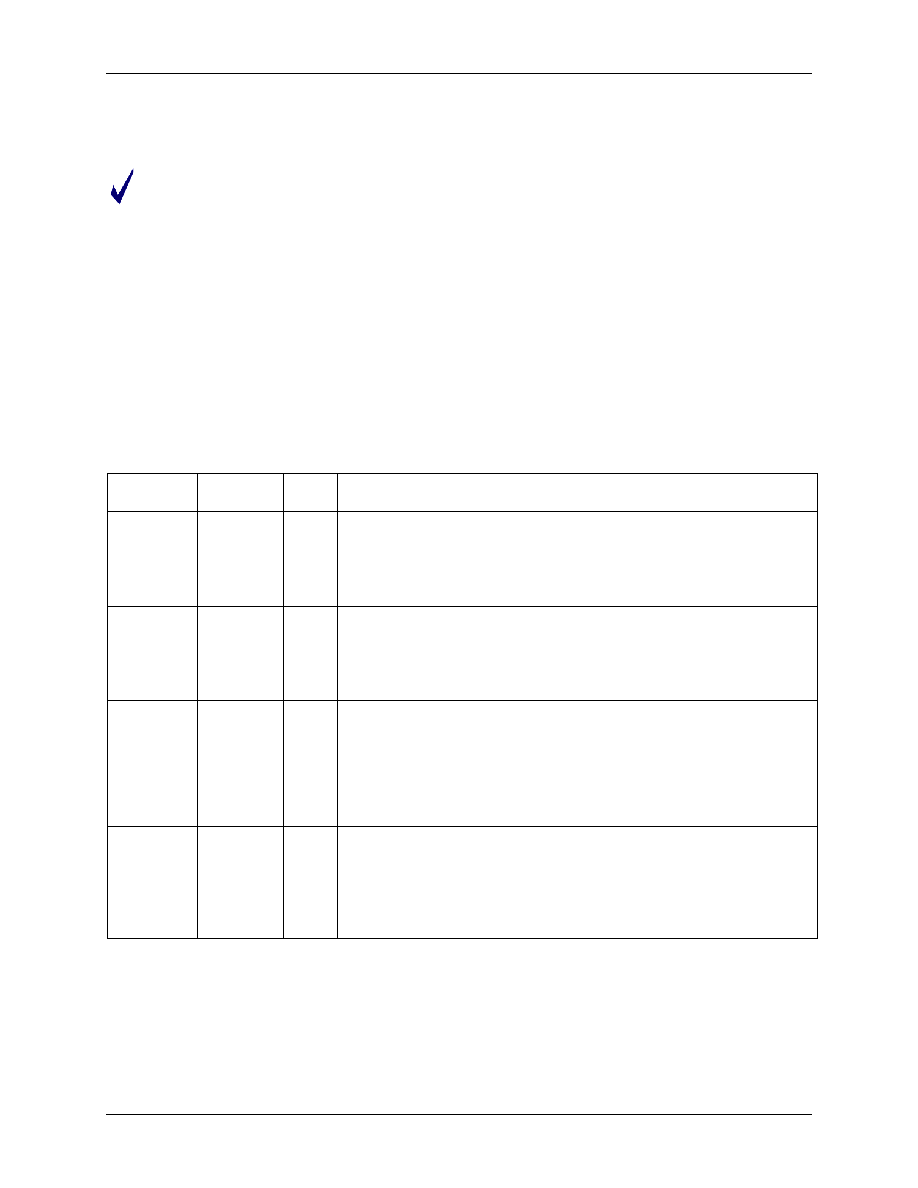

Function

Mnemonic

Register

Location

Type

Description

DIR

0x04[7:5]

W

GPIO Input/Output Select

These control bits are used to designate the GPIO pins as either

inputs or outputs.

0 = GPIO pin is defined as an output.

1 = GPIO pin is defined as an input. (Default)

GPIOn

0x03[7:5]

W

GPIO State

These bits reflect the status of the GPIO7, GPIO6 and GPIO5 pins.

If the DIR bit is reset, reading this field returns the logical value of the

appropriate GPIOn pin as an input.

If the DIR bit is set, the pins output the logical value as written.

ENGPIOn

0x05[7:5]

W

GPIO Enable

Each of the GPIO enable bits in this register enables the

corresponding GPIO bit as an edge-triggered interrupt source. If a

GPIO bit is set to one, an edge (which edge depends on the value in

the GIP register) of the corresponding GPIO pin will cause the

INT pin

to go active low, and the edge detectors will be rearmed when the

GPIO data register is read.

POLn

0x06[7:5]

W

GPIO Interrupt Edge Selection

Defines the interrupt source as being either on a rising or a falling

edge of the corresponding GPIO pin.

0 = A rising edge will trigger an interrupt from the corresponding pin.

(Default)

1 = A falling edge will trigger an interrupt from the corresponding pin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPS2D221MRD6 | CAP ALUM 220UF 200V 20% RADIAL |

| 73M1822-KEYCHN | BOARD KEYCHAIN 73M1822 42-QFN |

| 78Q2133-DB | EVAL BOARD 78Q2133 |

| MAX14821EVKIT# | EVAL KIT MAX14821 |

| UVZ1C472MHD | CAP ALUM 4700UF 16V 20% RADIAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73M1902-IM/F | 功能描述:電信線路管理 IC MicroDAA Chip Set Host Side RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| 73M1902-IMR/F | 功能描述:電信線路管理 IC MicroDAA Chip Set Host Side RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| 73M1902-IVT/F | 功能描述:電信線路管理 IC MicroDAA Chip Set Host Side RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| 73M1902-IVTR/F | 功能描述:電信線路管理 IC MicroDAA Chip Set Host Side RoHS:否 制造商:STMicroelectronics 產(chǎn)品:PHY 接口類型:UART 電源電壓-最大:18 V 電源電壓-最小:8 V 電源電流:30 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:VFQFPN-48 封裝:Tray |

| 73M1903 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Soft Modem AFEs |

發(fā)布緊急采購,3分鐘左右您將得到回復。