- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369276 > 73M2910L (Electronic Theatre Controls, Inc.) Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | 73M2910L |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 25/35頁 |

| 文件大?。?/td> | 572K |

| 代理商: | 73M2910L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

73M2910L

Microcontroller

25

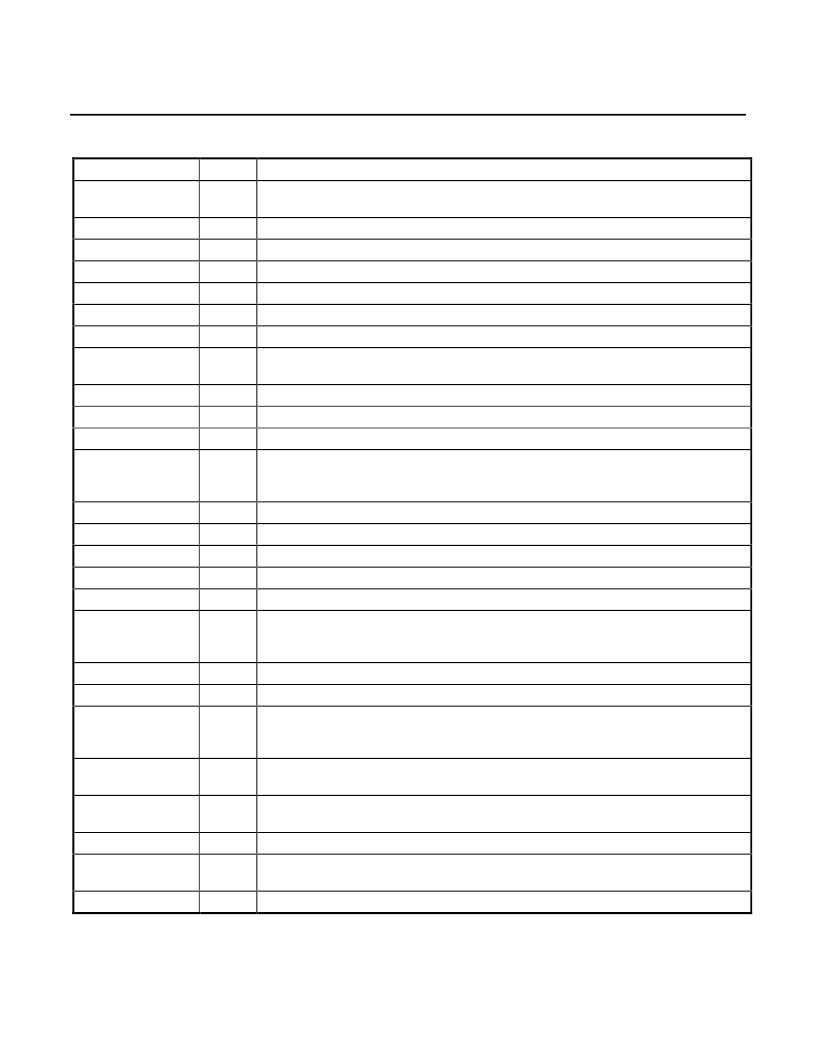

PIN DESCRIPTION

NAME

TYPE

DESCRIPTION

PSEN

O

Program store enable. This output occurs only during a fetch to external

program memory.

RESET

I

Input which is used to initialize the processor.

VND

GND

Negative digital voltage ground

OSCIN

I

Crystal input for internal oscillator, also input for external source.

OSCOUT

O

Crystal oscillator output.

VPD

I

Positive digital voltage (+5V Digital Supply)

CLKOUT1

O

Clock output programmable either OSC/2, OSC/1 or logic 0.

CLKOUT2

O

Clock output 1.8432 MHz clock for an external UART given an oscillator

frequency of 11.0592 MHz, 22.1184 MHz, 18.432 MHz, or 13.824 MHz.

TXD

I

Serial input port to 73M2910L from DTE same as RXD UART input.

RXD

O

Serial output port of 73M2910L UART to DTE.

PTXCLK

I

Input clock used to transmit data PTXD.

PTXD

O

HDLC Packetizer TX output. This pin can also be programmed to the DTE’s

TXD output (clear channel) or the value written into bit 6 of the HDLC Control

Register. Connects to modem device TXD.

PRXCLK

I

Input clock used to receive data PRXD.

PRXD

INT

(

)

)-

INT

(

@

)

I

Serial input port (from modem device) to HDLC Packetizer.

I

External interrupt 0,1 and 2.

USR1.0 - USR1.7

I/O

USR programmable I/O port.

USR2.0 - USR2.7

I/O

USR programmable I/O port.

USR3.0 - USR3.7

I/O

USR programmable I/O port. If the bank select feature is chosen, USR (7) acts

as address bit 17 and USR3 data bit 7 is ignored. Register BNKSEL bit 2 (BSEN)

enables bank select, bit 1 (BS1) and bit 0 (BS0) select the appropriate bank.

USR4.0 - USR4.7

I/O

USR programmable I/O port also chip select enable.

USR5.0 - USR5.1

I/O

General purpose input port, can also be used for wakeup.

RD

O

Output strobe activated during a bus read. Can be used to enable data onto

the bus from an external device. Used as a read strobe to external data

memory.

WR

O

Output strobe during a bus write. Used as a write strobe to external data

memory.

ALE

O

Address Latch Enable output pulse for latching the low byte of the address

during accesses to external memory.

AD(0)-AD(7)

I/O

Data bus lines-I/O for devices that require multiplexed address and data bus.

A(0)-A(15)

O

Address bus lines-output latched address for devices that require separate

data and address bus.

NO CONNECTS(NC)

No connections, leave open. Not a user pin.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73M2921 | Advanced Single Chip Modem |

| 73M2921-IG | Advanced Single Chip Modem |

| 7401 | Quad 2-Input NAND Gates with Open-Collector Outputs |

| 7404 | TRIPLE VOLTAGE REGULATOR |

| 7404 | Package contains six inverters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73M2910L-IG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| 73M2921 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Advanced Single Chip Modem |

| 73M2921-IG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Advanced Single Chip Modem |

| 73M2AR0015F | 功能描述:RES 0.0015 OHM 1% 2W 2512 制造商:cts resistor products 系列:73M2A 包裝:帶卷(TR) 零件狀態(tài):在售 電阻值:1.5 MOhms 容差:±1% 功率(W):2W 成分:金屬薄膜 特性:電流檢測(cè) 溫度系數(shù):±100ppm/°C 工作溫度:-55°C ~ 155°C 封裝/外殼:2512(6432 公制) 供應(yīng)商器件封裝:2512 大小/尺寸:0.248" 長(zhǎng) x 0.126" 寬(6.30mm x 3.20mm) 高度 - 安裝(最大值):0.043"(1.10mm) 端子數(shù):2 故障率:- 標(biāo)準(zhǔn)包裝:4,000 |

| 73M2AR001F | 功能描述:RES 0.001 OHM 1% 2W 2512 制造商:cts resistor products 系列:73M2A 包裝:帶卷(TR) 零件狀態(tài):在售 電阻值:1 MOhms 容差:±1% 功率(W):2W 成分:金屬薄膜 特性:電流檢測(cè) 溫度系數(shù):±100ppm/°C 工作溫度:-55°C ~ 155°C 封裝/外殼:2512(6432 公制) 供應(yīng)商器件封裝:2512 大小/尺寸:0.248" 長(zhǎng) x 0.126" 寬(6.30mm x 3.20mm) 高度 - 安裝(最大值):0.043"(1.10mm) 端子數(shù):2 故障率:- 標(biāo)準(zhǔn)包裝:4,000 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。