- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16271 > 78Q8430EBST#DB (Maxim Integrated Products)EVAL BOARD 78Q8430 PDF資料下載

參數(shù)資料

| 型號: | 78Q8430EBST#DB |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 79/88頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD 78Q8430 |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁當前第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

78Q8430 Data Sheet

DS_8430_001

80

Rev. 1.2

7.7.9

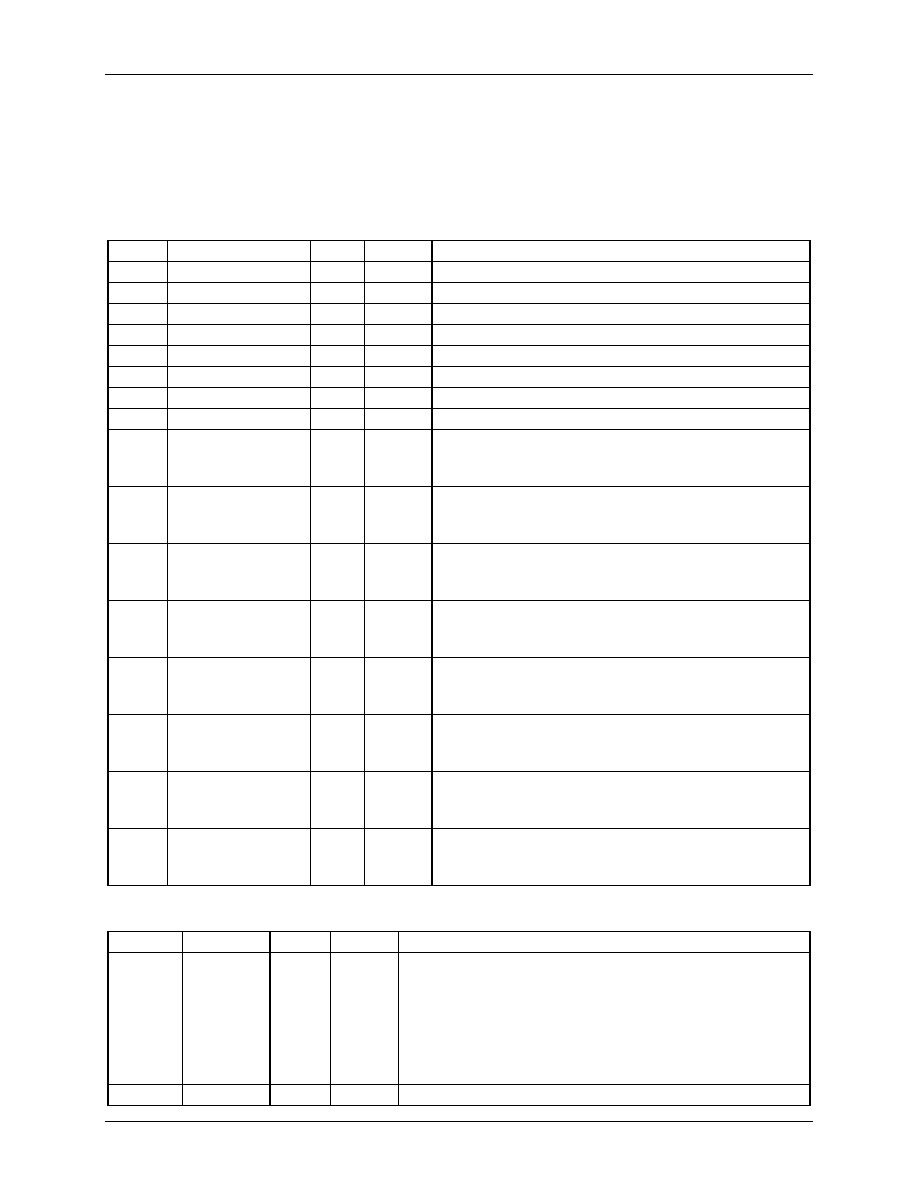

PHY Interrupt Control / Status Register – MR17

The Interrupt Control/Status Register provides the means for controlling and observing the events that

trigger an interrupt on the internal PHY interrupt signal. This register can also be used in a polling mode

via the MII Serial Interface as a means to observe key events within the PHY via one register address.

Bits 0 through 7 are status bits, which are each set to logic one based upon an event. These bits are

cleared after the register is read. Bits 8 through 15 of this register, when set to logic one, enable their

corresponding bit in the lower byte to signal an interrupt on the PHY interrupt signal.

Bits

Symbol

Type

Default Description

15

JABBER_IE

R/W

0

Jabber Interrupt Enable

14

RXER_IE

R/W

0

Receive Error Interrupt Enable

13

PRX_IE

R/W

0

Page Received Interrupt Enable

12

PDF_IE

R/W

0

Parallel Detect Fault Interrupt Enable

11

LP_ACK_IE

R/W

0

Link Partner Acknowledge Interrupt Enable

10

LS_CHANGE_IE

R/W

0

Link Status Change Interrupt Enable

9

RFAULT_IE

R/W

0

Remote Fault Interrupt Enable

8

ANEG-COMP_IE

R/W

0

Auto-Negotiation Complete Interrupt Enable

7

JAB_INT

RC

0

Jabber Interrupt

This bit is set high when a Jabber event is detected by

the 10Base-T circuitry.

6

RXER_INT

RC

0

Receive Error Interrupt

This bit is set high when the RX_ER signal transitions

high.

5

PRX_INT

RC

0

Page Received Interrupt

This bit is set high when a new page has been

received from the link partner during auto-negotiation.

4

PDF_INT

RC

0

Parallel Detect Fault Interrupt

This bit is set high by the auto-negotiation logic when a

parallel detect fault condition is indicated.

3

LP_ACK_INT

RC

0

Link Partner Acknowledge Interrupt

This bit is set high by the auto-negotiation logic when

FLP bursts are received with the acknowledge bit set.

2

LS_CHANGE_INT

RC

0

Link Status Change Interrupt

This bit is set when the link status transitions from an

OK status to a FAIL status, or vice versa.

1

RFAULT_INT

RC

0

Remote Fault Interrupt

This bit is set when a remote fault condition is

detected.

0

ANEG_COMP_INT

RC

0

Auto-Negotiation Complete Interrupt

This bit is set by the auto-negotiation logic upon

completion of auto-negotiation.

7.7.10 PHY Transceiver Control Register – MR19

Bit

Symbol

Type

Default Description

15:14

TXO[1:0]

R/W

01

Transmit Amplitude Selection

Sets the transmit output amplitude to account for transmit

transformer insertion loss.

00 = Gain set for 0.0dB of insertion loss

01 = Gain set for 0.4dB of insertion loss

10 = Gain set for 0.8dB of insertion loss

11 = Gain set for 1.2dB of insertion loss

13:0

RSVD

R/W

XXX

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CM453232-R18KL | INDUCTOR 180NH 700MA SMD |

| REC15-1205D/H3 | CONV DC/DC 15W 12VIN +/-05VOUT |

| VI-JWL-EZ-F3 | CONVERTER MOD DC/DC 28V 25W |

| A3BKB-2406G | IDC CABLE- ASR24B/AE24G/APK24B |

| REC15-2415D/H3 | CONV DC/DC 15W 24VIN +/-15VOUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 78Q8430STEM#DB | 功能描述:以太網(wǎng)開發(fā)工具 3-in-1 Silicon Delay Line RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

| 78-R3 | 功能描述:3M SCOTCHCAST REENTERABLE SIGNAL 制造商:3m 系列:* 零件狀態(tài):在售 標準包裝:1 |

| 78-R4 | 功能描述:3M SCOTCHCAST REENTERABLE SIGNAL 制造商:3m 系列:* 零件狀態(tài):在售 標準包裝:1 |

| 78RB02 | 功能描述:SWITCH 2 POS DIP RECESSED UNSLD RoHS:否 類別:開關(guān) >> DIP 系列:78 特色產(chǎn)品:RDM Series Rotary DIP Switch 標準包裝:70 系列:RDM 電路:十六進制 位置數(shù):16 觸點額定電壓:0.1A @ 42VDC 觸動器類型:用于工具旋轉(zhuǎn) 觸動器電平:凹槽式 安裝類型:通孔 方向:頂部觸動 可清洗:是 其它名稱:EG4977-5RDMAR16PIT |

| 78RB02RA | 制造商:Grayhill 功能描述:DIP, 2 POS, FLUSH ACTUATOR, SPST, GOLD - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。