- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366329 > ACE9050 (Mitel Networks Corporation) System Controller and Data Modem Advance Information PDF資料下載

參數(shù)資料

| 型號(hào): | ACE9050 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | System Controller and Data Modem Advance Information |

| 中文描述: | 系統(tǒng)控制器和數(shù)據(jù)調(diào)制解調(diào)器進(jìn)展信息 |

| 文件頁(yè)數(shù): | 24/52頁(yè) |

| 文件大?。?/td> | 390K |

| 代理商: | ACE9050 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

ACE9050

24

7. CLOCK GENERATOR

The AC9050 provides a clock generator with crystal oscillator

circuit. This circuit generates all of the chip clock frequencies to

which the logic is synchronised. In Normal mode all the clocks

are generated from one external source. In Emulation mode the

Master clock is the ECLK which becomes an input.

For AMP and TACS mobile handset applications the input

frequency must be 8·064MHz. In Emulation Mode an input

frequency of 1·008MHz, or 2·016MHz in Turbo mode, is required

on the ECLK pin. Note that, although the ACE9050 will operate

with lower frequencies, the radio functions such as the Modem

would not then function correctly in a radio system.

The clock generator has a built-in oscillator which requires an

external crystal. Alternatively, the oscillator can be powered

down and either a 800mv peak-to-peak AC-coupled sinewave or

a CMOS logic level applied to XIN may be used. If the ACE9030

is being used this provides a suitable output via CLK8; AC

coupling must be used.

The main internal clock (1·008MHz) is derived from the CPU

clock, or ECLK. This can either be 1·008 MHz or 2·016 MHz in

Turbo mode. In Turbo mode ECLK is divided by 2 to generate the

main 1·008MHz clock. This gives correct functionality when in

Emulation mode, where the ECLK frequency is generated

externally.

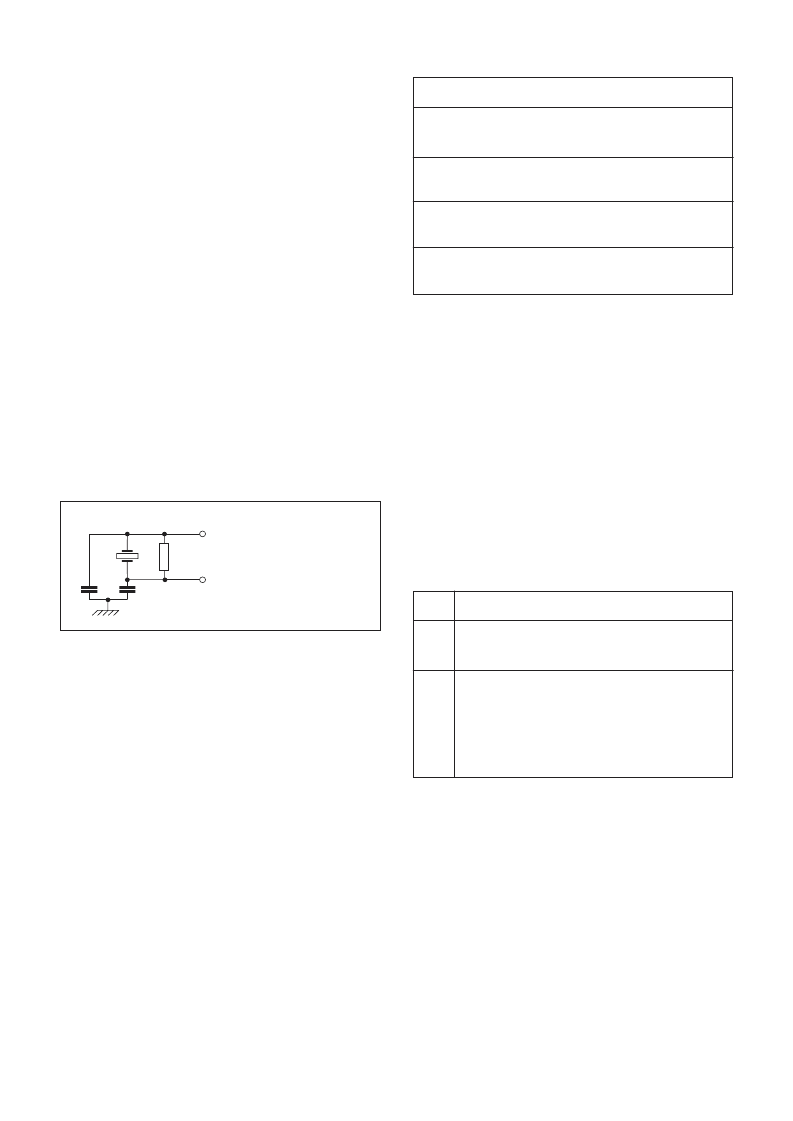

The clock generator produces a clock bus with all of the

internal clock frequencies required by the ACE9050. Various

frequencies are also available externally . If an external crystal is

used with the Crystal Oscillator, Fig. 17 shows the external

components required. Careful layout rules should be applied to

the external Crystal Circuit design. These include mounting the

components as close as possible to the ACE9050 and avoiding

running signal lines close to the oscillator circuit.

External Pins

CPUCL

8·064 MHz Output (pin 94)

This output is the buffered crystal or clock input frequency.

After reset it is disabled, but can be enabled by software. Refer

to Associated Registers.

C1008

1·008 MHz Output (pln 90)

This output is the main clock divided by eight. It must always

be 1·008 MHz in a mobile phone application using the ACE

chipset. It is intended to drive the ACE Serial interface clock. It is

enabled after reset, but can be disabled by software.

ECLK

Processor Clock (pin 99)

This is the processor clock. It is an output in Normal mode, but

an input in Emulation. The frequency is 1·008MHz, or 2·01 6MHz

in Turbo mode.

XIN

Crystal or External source (pin 2)

Input Crystal or external source input. External source must

be AC-coupled or CMOS levels.

XOUT

Crystal Output (pin 3)

If an external crystal is used connect between XIN and XOUT.

If an external source s used this output should be eft unconnected.

Associated Registers

Description

Table 37

8. BAUD RATE GENERATOR

The Baud Rate Generator provides standard baud rate

clocks for the SCI in the 6303 block. It is internally connected to

the 6303 Port2 bit 2. For Emulation mode the Baud Rate

generator clock output is available to drive the shadow 6303. The

Baud rate clock output is 8 times the baud rate. This is the

requirement for a standard 6303. Baud rates available are

shown in Table 38.

For higher baud rates a 6303 transfer rate can be selected in

the TRCSR register. As these are referenced to the ECLK they

will be non-standard rates.

External Pins

BAUDCLK:

Baud rate clock output. (pin 6)

This output is 8

3

the baud rate. It is used in emulation mode

only by the shadow 6303.

Associated Registers

BRG:

Baud rate Select port - Write only

TURBO: Port 4 bit 3

0 = 1·008MHz (Reset state)

1 = 2·016MHz (Turbo)

ENSIS: Port 3 bit 2

0 = CPUCL pin: OUT2 [0] (Reset state)

1 = CPUCL pin: 8·064MHz

CLKENAB: Port 5 bit 1

0 = C1008 pin = 0

1 = C1008 pin = 1·008MHz (Reset state)

XOSC PD: Port 5 bit 6

0 = Oscillator active (Reset state)

1 = Oscillator power down

Bits

[7: 3]

XXXX

[2: 0]

000

001

010

011

100

Description

Unused

600 Baud (Reset state)

1200 Baud

2400 Baud

4800 Baud

9600 Baud

Table 38

R1 = 470k

to 1M

C1, C2 = 22pF typical

(Refer to AC

Characteristics)

X1

R1

C1

C2

XIN

XOUT

2

3

Fig. 17 External crystal components

9. EXTERNAL RESET AND WATCHDOG FUNCTION

The ACE9050 contains a Master reset circuit. Upon a reset

being applied, all the circuits are reset and the registers put into

a known state. These are detailed in Tables 8 and 9 for the

ACE9050 and 6303 registers respectively. The mode selection

of the 6303 also occurs automatically upon Master reset. An

external output (EXRESN) is also asynchronously driven low.

The Master reset circuit is activated by one of two means:

(a) The external pin MRN (Master Reset) being driven low.

(b) Watchdog Time out.

The Watchdog circuit provides an automatic means to reset

the processor if it gets stuck in an infinite loop, which would be

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ACFA-450 | AM CERAMIC FILTERS |

| ACFA-455 | AM CERAMIC FILTERS |

| ACFA-459 | AM CERAMIC FILTERS |

| ACFA-468 | AM CERAMIC FILTERS |

| ACFJW-450A | AM CERAMIC FILTERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACE9050C/IW/FP1N | 制造商:Microsemi Corporation 功能描述:PB FREE SYSTEM CONTROLLER & DATA MODEM - Bulk |

| ACE9050C/IW/FP1Q | 制造商:Microsemi Corporation 功能描述:PB FREE SYSTEM CONTROLLER & DATA MODEM - Bulk |

| ace9050c/iw/fp8q | 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

| ace9050d/ig/gp1n | 制造商:Microsemi Corporation 功能描述:CNTRLR AND DATA MODEM 100LQFP - Bulk 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

| ACE9050D/IG/GP2N | 制造商:Microsemi Corporation 功能描述:CNTRLR AND DATA MODEM 100LQFP - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。