- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366329 > ACE9050 (Mitel Networks Corporation) System Controller and Data Modem Advance Information PDF資料下載

參數(shù)資料

| 型號: | ACE9050 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | System Controller and Data Modem Advance Information |

| 中文描述: | 系統(tǒng)控制器和數(shù)據(jù)調(diào)制解調(diào)器進展信息 |

| 文件頁數(shù): | 35/52頁 |

| 文件大小: | 390K |

| 代理商: | ACE9050 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ACE9050

35

Bit

Function

0 = Discriminator enabled

1 = Discriminator bypassed (test)

4

Name

LF1_2

Associated Register bits

LF1_2

MODPRT 1[4] (Table 67)

Table 67

For test purposes the discriminator can be bypassed. This is

achieved by setting LF1_2. In this case the Modem requires

10kHz or 8kHz Manchester encoded data, i.e. the baseband

data signal.

RXDINV

MODPRT 1[5] (Table 68)

Bit

Function

0 = RX Data not inverted

1 = RX Data inverted

5

Name

RXDINV

Table 68

The phase of the Data from the Discriminator is determined

by the RF architecture of the receiver. The data can be inverted

to cater for both high side and low side VCO architectures.

Data Decoder

The Data Decoder is responsible for clock and data extraction

from the discriminated baseband Manchester encoded data

stream. Manchester encoded data inherently contains the clock.

The Data Decoder extracts the clock timing from the incoming

data stream and regenerates an appropriately phased clock.

The circuit then EXORs the extracted clock with the data. This

yields a 1 for the bit period if the data bit is in phase, or a 0 if the

data is out of phase. It then samples the output from the EXOR

at 504kHz.

Thus, nominally 50·4 or 63 samples are taken per bit period

for AMPS or TACS respectively. The data decoder will then

decide if the bit is a 1 or a 0, on the state with the highest number

of samples. If the number of ‘correct’ samples is over a certain

threshold then a flag is set. The required threshold can be set by

software and is referred to as the squelch level. The flag is

passed to the Word Sync Detector along with the value of the bit.

The Data Decoder uses a digital transition tracking loop to

regenerate the correctly phased clock. A clock at 90 degrees to the

data extraction clock and an integrate-and-dump function are used.

This 90 degree clock is again EXORed with the incoming data

stream. The result of this is fed into an up/down counter. The output

of the counter, along with the bit value, will determine whether the

phase of the incoming clock was early or late. The phase of the clock

over the next bit period will be altered to pull the clock in the

appropriate direction. This process repeats for every bit period. The

amount the clock is pulled is determined by the SYNDET bit.

Manchester encoded data transitions occur on the bit boundaries

as well as in the centre of the bit. This is especially true for a string

of 1s or 0s. There is a chance the clock will lock on to these, 180

degrees out of phase. The word structure contains a dotting

sequence; this is a 1010… pattern which is devoid of incorrect

transitions. The hardware can recognise the error condition during

this time and automatically correct the clock phase.

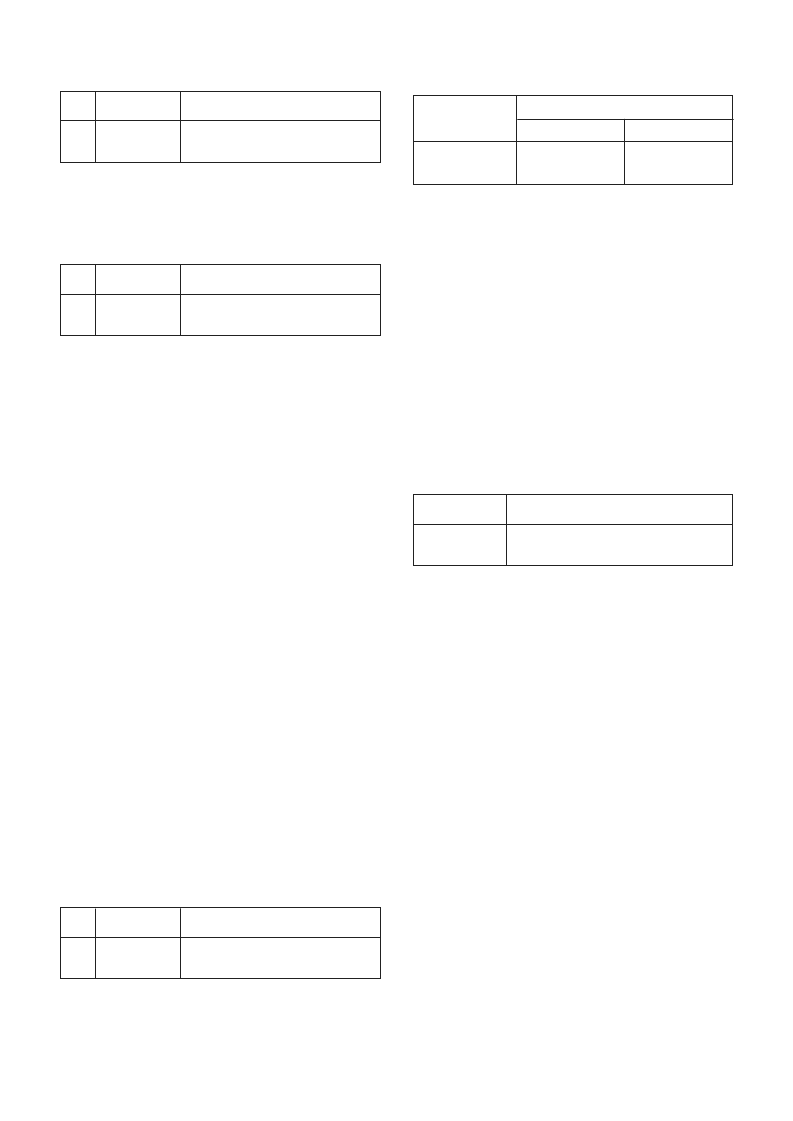

Bit

Function

0 = Capture mode

1 = Sync mode

2

Name

SYNDET

Associated Registers

SYNDET

MODPRT 0 [2] (Table 69)

Table 69

The digital tracking loop can be configured in two modes:

Capture or Sync, as detailed in Table 70.

Regenerated clock shift

Mode

TACS (125

μ

s)

AMPS (100

μ

s)

0 = Capture mode

1 = Sync mode

6

4% (12

μ

s)

6

1·6% (4

μ

s)

6

5% (10

μ

s)

6

1% (2

μ

s)

Table 70

In Capture mode the regenerated clock is shifted by a greater

percentage of the cycle than in Sync mode. This will allow the

regenerated clock to slip over and then acquire the incoming

clock phase faster. For example, to re-acquire phase in the

AMPS system would take around 2ms with good signal levels.

In Sync mode the regenerated clock is not shifted as much,

allowing more accurate data extraction over the bit period. If the

regenerated clock becomes out of phase in this mode it will of

course take longer to re-acquire the correct phase. For example

in the AMPS system, to re-acquire phase would take around

10ms.

The clock rate for the circuit is 504kHz, hence the circuit works

to a resolution which is a multiple of 2

μ

s in all cases. In general,

the SYNDET bit should be set to Capture mode until the system

design is satisfied that the Modem is in Word Sync. Then the

SYNDET should be switched to Sync mode before data reading

begins.

NOMPLL

Nominal PLL Port 4 [5]

The Digital Tracking loop’s operation can be turned on or off

with the NOMPLL bit, as shown in Table 71.

0

1

NOMPLL

Table 71

Data Clock synchronising enabled

Data Clock free-running

Mode

The NOMPLL bit will generally be set to 0 to allow normal

operation of the digital tracking loop and clock synchronisation

circuit.

With NOMPLL set to 1 the regenerated clock will not try to lock

to the incoming data clock, but will keep its current phase. If there

is a short period of time when data is not present it may be

advantageous to set the NOMPLL bit. The Digital trackinq loop

will then be prevented from ‘hunting’ for a non-existent data

clock. When the data then reappears, the regenerated clock

should still be in phase and data can be immediately decoded

without the need to re-synchronise. This facility is of use in

systems where the receiver can power down for short periods of

time in Standby mode, thus reducing the overall current

consumption of the phone unit.

SQLEV [3: 0]

MODPRT1 [3:0]

The software can set a ‘squelch level’ for the incoming data.

This sets the number of samples of a bit that have to be ‘correct’

for the bit to be approved. The Data Decoder sets a flag at the end

of a bit period if the squelch level has been reached. The Word

Sync Detector then sums the number of approved bits that occur

in a byte and updates the SQRX register at the same time as the

data register.

Four bits are used to determine the squelch threshold, giving

16 different levels. The number of samples for AMPS and TACS

systems is 50 and 63 respectively.

Table 72 on the following page shows the number of samples

required for a bit to meet the level set, and the percentage of the

total number of samples for both AMPS and TACS settings that

this represents.

相關PDF資料 |

PDF描述 |

|---|---|

| ACFA-450 | AM CERAMIC FILTERS |

| ACFA-455 | AM CERAMIC FILTERS |

| ACFA-459 | AM CERAMIC FILTERS |

| ACFA-468 | AM CERAMIC FILTERS |

| ACFJW-450A | AM CERAMIC FILTERS |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ACE9050C/IW/FP1N | 制造商:Microsemi Corporation 功能描述:PB FREE SYSTEM CONTROLLER & DATA MODEM - Bulk |

| ACE9050C/IW/FP1Q | 制造商:Microsemi Corporation 功能描述:PB FREE SYSTEM CONTROLLER & DATA MODEM - Bulk |

| ace9050c/iw/fp8q | 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

| ace9050d/ig/gp1n | 制造商:Microsemi Corporation 功能描述:CNTRLR AND DATA MODEM 100LQFP - Bulk 制造商:Rochester Electronics LLC 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述: |

| ACE9050D/IG/GP2N | 制造商:Microsemi Corporation 功能描述:CNTRLR AND DATA MODEM 100LQFP - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。