- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄165344 > ADAU1382BCPZ (ANALOG DEVICES INC) SPECIALTY CONSUMER CIRCUIT, PQCC32 PDF資料下載

參數(shù)資料

| 型號: | ADAU1382BCPZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQCC32 |

| 封裝: | 5 X 5 MM, ROHS COMPLIANT, MO-220VHHD2, LFCSP-32 |

| 文件頁數(shù): | 51/84頁 |

| 文件大?。?/td> | 1193K |

| 代理商: | ADAU1382BCPZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當(dāng)前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

ADAU1382

Rev. 0| Page 55 of 84

Register 16406 (0x4016), Serial Port Control 1

Bits[7:5], Number of Bit Clock Cycles per Frame

These bits set the number of BCLK cycles contained in one

LRCLK period. The frequency of BCLK is calculated as the

number of bit clock cycles per frame times the sample rate of

of different settings for these bits.

Bit 4, ADC Channel Position in TDM

This register sets the order of the ADC channels when output on

the serial output port. A setting of 0 puts the left channel first in its

respective TDM channel pair. A setting of 1 puts the right channel

first in its respective TDM channel pair. This bit should be set in

conjunction with Register 16408 (0x4018), Converter Control 1,

Bits[1:0], on-chip ADC data selection in TDM mode, to select

where the data should appear in the TDM stream. Figure 62 shows

a setting of 0, and Figure 63 shows a setting of 1.

Bit 3, DAC Channel Position in TDM

This register sets the order of the DAC channels when output on

the serial output port. A setting of 0 puts the left channel first in its

respective TDM channel pair. A setting of 1 puts the right channel

first in its respective TDM channel pair. This bit should be set in

conjunction with Register 16407 (0x4017), Converter Control 0,

Bits[6:5], on-chip DAC data selection in TDM mode, to select

where the data should appear in the TDM stream. Figure 62

shows a setting of 0, and Figure 63 shows a setting of 1.

Bit 2, MSB Position

This bit sets the bit-level endianness (or bit order) of the data

stream. A setting of 0 results in a big-endian order, with the MSB

coming first in the stream and the LSB coming last. A setting of 1

results in a little-endian order, with the LSB coming first in the

stream and the MSB coming last. Figure 64 shows examples of

the two settings with a 24-bit audio stream in an MSB delay-by-0

configuration. In Figure 64, M stands for MSB, and L stands for LSB.

Bits[1:0], Data Delay from LRCLK Edge

These bits set the delay between the LRCLK edge and the first

data bit in the stream. The I2S standard is a delay of one BCLK

cycle. Examples of different data delay settings are shown

in Figure 65, with a 64 BCLK cycle per frame, 24-bit audio data,

big-endian bit order configuration. In Figure 65, M represents

the most significant bit of the audio channel’s data, and L represents

the least significant bit.

The first example setting (delay by 0) in Figure 65 represents a left-

justified mode because the least significant bit aligns with the

beginning of the audio frame. The third example setting (delay

by 8) represents a right-justified mode because the least significant

bit aligns with the end of the audio frame. A delay-by-16 setting

would not be valid in this mode because the audio data would

exceed the boundaries of the frame clock period.

Figure 66 shows an example of delay by 16 for a 16-bit audio

stream with 64 BCLK cycles per frame.

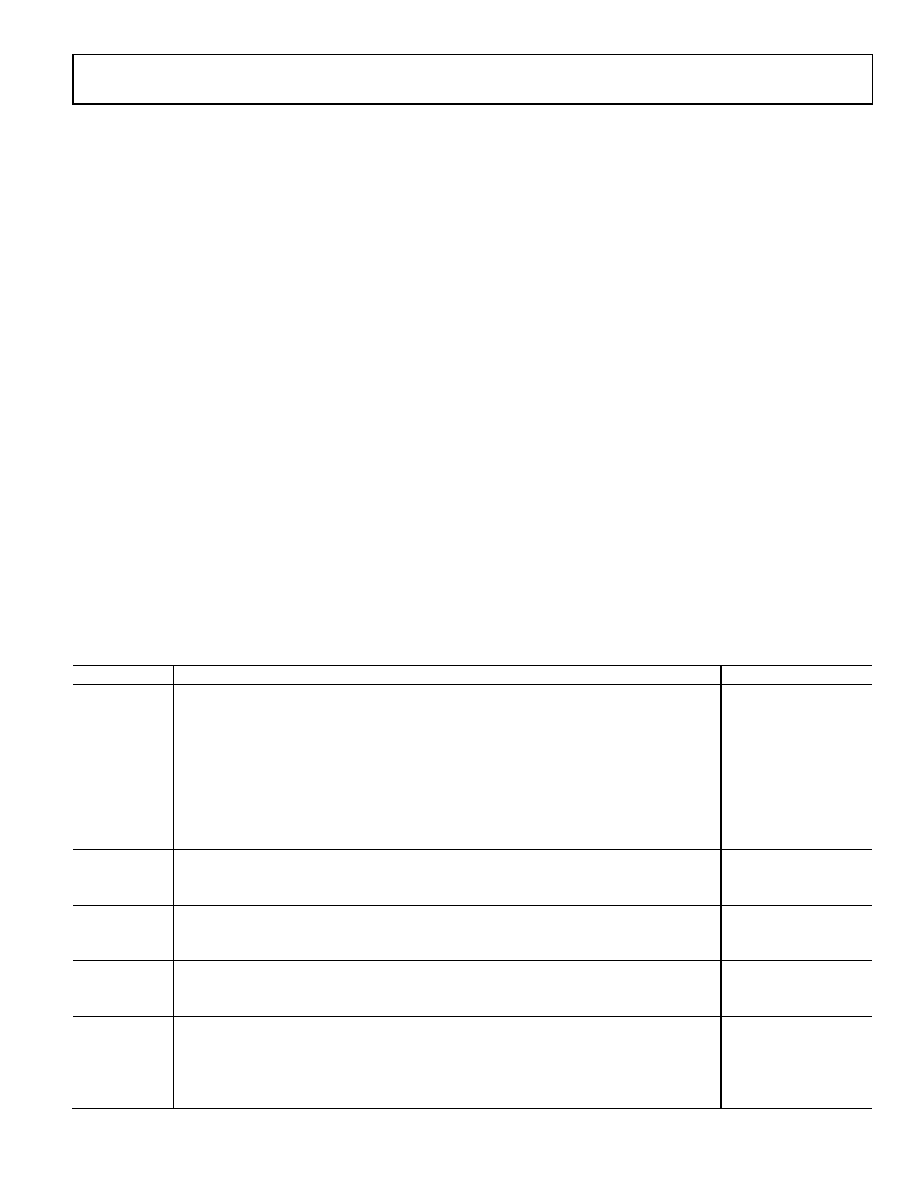

Table 41. Serial Port Control 1 Register

Bits

Description

Default

[7:5]

Number of bit clock cycles per frame

000

000: 64

001: 32

010: 48

011: 128

100: 256

101: reserved

110: reserved

111: reserved

4

ADC channel position in TDM

0

0: left first

1: right first

3

DAC channel position in TDM

0

0: left first

1: right first

2

MSB position

0

0: MSB first

1: MSB last

[1:0]

Data delay from LRCLK edge

00

00: 1 BCLK cycle

01: 0 BCLK cycles

10: 8 BCLK cycles

11: 16 BCLK cycles

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADC-00403-103 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP32 |

| ADC0831 | A/D Peripherals with Serial Control |

| ADC0831A | A/D Peripherals with Serial Control |

| ADC0831B | A/D Peripherals with Serial Control |

| ADC0832 | A/D Peripherals with Serial Control |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADAU1382BCPZ-R7 | 制造商:Analog Devices 功能描述:STEREO AUDIO CODEC FOR DIG STILL CAM - Tape and Reel 制造商:Analog Devices 功能描述:AUDIO CODEC |

| ADAU1401 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401A | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1401AWBSTZ | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標(biāo)準(zhǔn)包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應(yīng)用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1401AWBSTZ-RL | 功能描述:IC AUDIO PROC 28/56BIT 48LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關(guān)文件:STA321 View All Specifications 標(biāo)準(zhǔn)包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應(yīng)用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應(yīng)商設(shè)備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。