- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄366891 > CR16HCT5VJE8Y Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | CR16HCT5VJE8Y |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 104/157頁(yè) |

| 文件大?。?/td> | 1256K |

| 代理商: | CR16HCT5VJE8Y |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)當(dāng)前第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)

www.national.com

104

20.7.2

The interrupt code IST[3:0] can be used within the interrupt

handler as a displacement in order to jump to the relevant

subroutine.

The CAN Interrupt Code Enable (CICEN) register is used in

the CAN interrupt handler if the user wants to service all re-

ceive buffer interrupts first followed by all transmit buffer in-

terrupts. In this case, the user can first enable only all receive

buffer interrupts to be coded, scan and service all pending in-

terrupt requests in the order of their priority. Then, the user

changes the CICEN register to disable all receive buffers, but

enable all transmit buffers and service all pending transmit

buffer interrupt requests according to their priorities.

Usage Hints

20.8

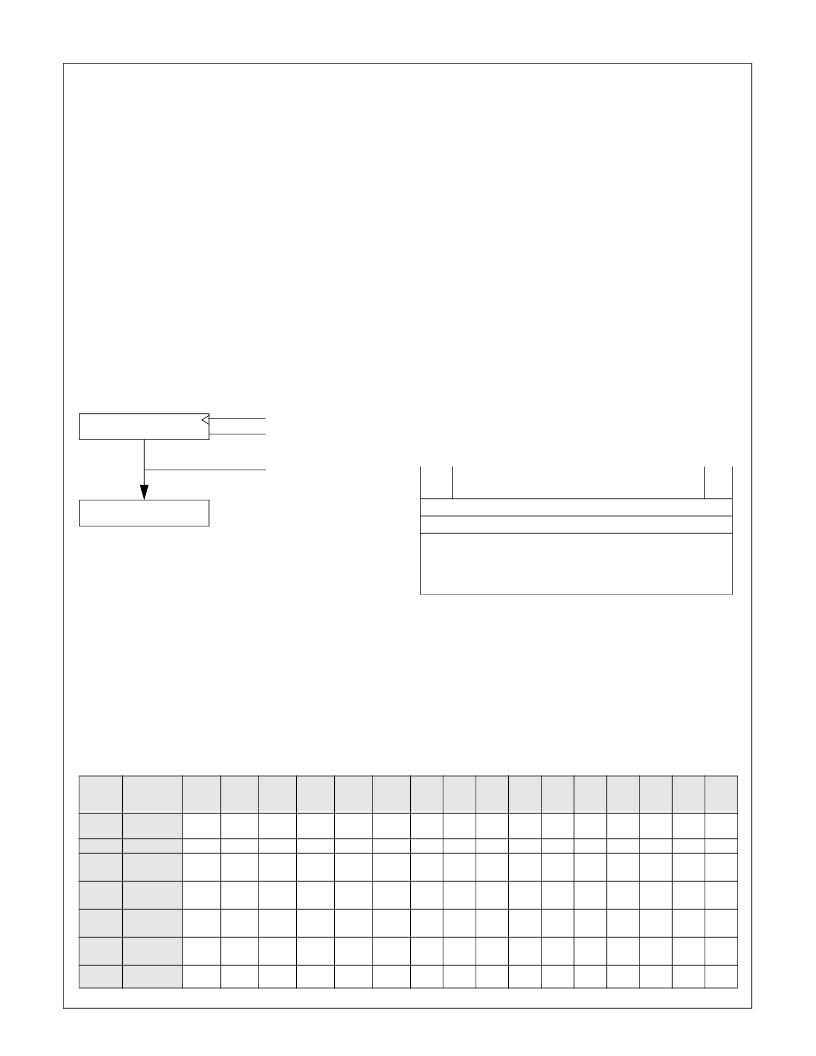

CR16CAN features a free running 16-bit timer (CTMR) incre-

menting every bit time recognized on the CAN bus. The value

of this timer during the ACK slot is captured into the TSTP

register of a message buffer after a successful transmission

or reception of a message. Figure 68 shows a simplified

block diagram of the Time Stamp counter.

TIME STAMP COUNTER

The timer can be synchronized over the CAN network by re-

ceiving or transmitting a message to/from buffer 0. In that

case the TSTP register of buffer 0 captures the current

CTMR value during the ACK slot of a message (as above)

and afterwards the CTMR is reset to 0000

2

. Synchronization

can be enabled or disabled via the CGCR.TSTPEN bit.

20.9

CR16CAN occupies 144 words in the memory address

space. This space is separated into 15*8 + 8(reserved) words

for the message buffers and 14 + 2(reserved) words for con-

trol and status.

MEMORY ORGANIZATION

20.9.1

All memory locations occupied by the message buffers are

shared by the CPU and CR16CAN (dual ported RAM). The

CR16CAN and the CPU normally have single cycle access to

this memory. However, if an access contention occurs, the

access to the memory is altered every cycle until the conten-

tion is resolved. This internal access arbitration is transparent

to the user.

Both word and byte access to the buffer RAM are allowed. If

a buffer is busy during the reception of an object (copy pro-

cess from the hidden receive buffer) or is scheduled for trans-

mission, the CPU has no write access to the data contents of

the buffer. Write to the status/control byte and read access to

the whole buffer is always enabled.

All configuration and status registers can either be accessed

by CR16CAN or the CPU only. These registers provide single

cycle word and byte access without any potential wait state.

All register descriptions within the next sections utilize the fol-

lowing layout:

bit

15

... bit name ...

... reset value ...

... CPU access ...

r = register bit is read only

w = register bit is write only

r/w = register bit is read/write

CPU Access to CR16CAN Registers/Memory

20.9.2

The message buffers are the communication interfaces be-

tween CAN and the CPU for the transmission and the recep-

tion of CAN frames. There are 15 message buffers located at

fixed addresses in the RAM location. As shown in Table 25,

each buffer consists of two words reserved for the identifiers,

4 words reserved for up to eight CAN data bytes, one word is

reserved for time stamp and one word for data length code,

transmit priority code and the buffer status code.

Message Buffer Organization

16-bit counter

TSTP register

CAN bits on the bus

ACK slot & buffer 0 active

ACK slot

+1

Reset

Figure 68.

Time Stamp Counter

... bit number ...

bit

0

Table 25

Message Buffer Organization

ADDR

BUFFER

register

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

xxxE

16

ID1

XI28

ID10

XI27

ID9

XI26

ID8

XI25

ID7

XI24

ID6

XI23

ID5

XI22

ID4

XI21

ID3

XI20

ID2

XI19

ID1

XI18

ID0

SRR

RTR

XI3

IDE

XI17

XI16

XI15

xxxC

16

ID0

XI14

XI13

XI12

XI11

XI10

XI9

XI8

XI7

XI6

XI5

XI4

XI2

XI1

XI0

RTR

xxxA

16

DATA0

Data

1.7

Data

Data

1.6

Data

Data

1.5

Data

Data

1.4

Data

Data

1.3

Data

Data

1.2

Data

Data

1.1

Data

Data

1.0

Data

Data

2.7

Data

Data

2.6

Data

Data

2.5

Data

Data

2.4

Data

Data

2.3

Data

Data

2.2

Data

Data

2.1

Data

Data

2.0

Data

xxx8

16

DATA1

3.7

Data

3.6

Data

3.5

Data

3.4

Data

3.3

Data

3.2

Data

3.1

Data

3.0

Data

4.7

Data

4.6

Data

4.5

Data

4.4

Data

4.3

Data

4.2

Data

4.1

Data

4.0

Data

xxx6

16

DATA2

5.7

Data

5.6

Data

5.5

Data

5.4

Data

5.3

Data

5.2

Data

5.1

Data

5.0

Data

6.7

Data

6.6

Data

6.5

Data

6.4

Data

6.3

Data

6.2

Data

6.1

Data

6.0

Data

xxx4

16

DATA3

7.7

7.6

7.5

7.4

7.3

7.2

7.1

TSTP

9

7.0

TSTP

8

8.7

TSTP

7

8.6

TSTP

6

8.5

TSTP

5

8.4

TSTP

4

8.3

TSTP

3

8.2

TSTP

2

8.1

TSTP

1

8.0

TSTP

0

xxx2

16

TSTP

TSTP15

TSTP14

TSTP13

TSTP12

TSTP11

TSTP10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CR16HCT5VJE9Y | Microcontroller |

| CR16HCT9 | |

| CR16HCT9VJE7 | Microcontroller |

| CR16HCT9VJE7Y | Microcontroller |

| CR16HCT9VJE8 | Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CR16HCT5VJE9Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

| CR16HCT5VJEXY | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16HCT9 | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:CR16MCT9/CR16MCT5/CR16HCT9/CR16HCT5 16-Bit Reprogrammable/ROM Microcontroller |

| CR16HCT9VJE7 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

| CR16HCT9VJE7Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。