- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373038 > DAC1008D750HN (NXP Semiconductors N.V.) Dual 10-bit DAC; up to 750 Msps; 2×, 4× or 8× interpolating PDF資料下載

參數(shù)資料

| 型號: | DAC1008D750HN |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | Dual 10-bit DAC; up to 750 Msps; 2×, 4× or 8× interpolating |

| 封裝: | DAC1008D750HN/C1<SOT804-3|<<<1<Always Pb-free,;DAC1008D750HN/C1<SOT804-3|<<<1<Always Pb-free,; |

| 文件頁數(shù): | 31/99頁 |

| 文件大小: | 547K |

| 代理商: | DAC1008D750HN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

DAC1008D750

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2011. All rights reserved.

Product data sheet

Rev. 2 — 5 January 2011

31 of 99

NXP Semiconductors

DAC1008D750

2

×

, 4

×

or 8

×

interpolating DAC with JESD204A

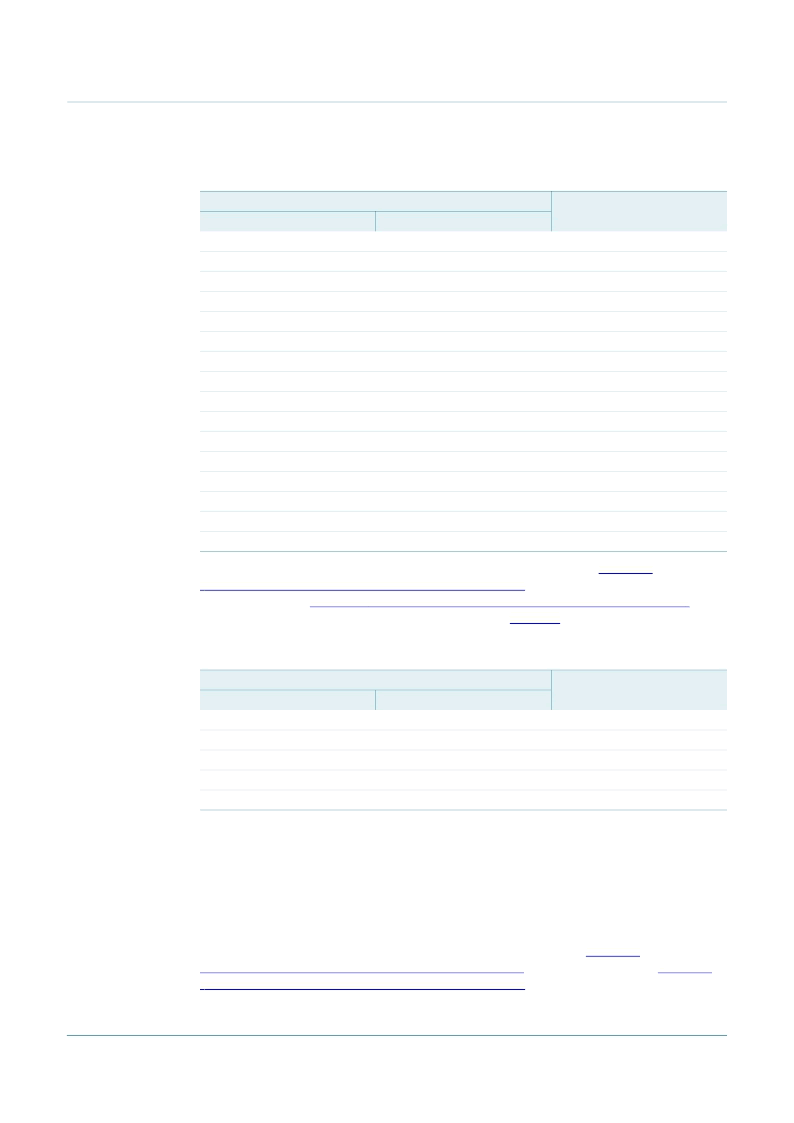

Table 13.

Default settings are shown highlighted.

DAC_GAIN_COARSE[3:0]

Decimal

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

The settings applied to DAC_A_GAIN_FINE[5:0] (register 0Ah; see

Table 28

“DAC_A_CFG_2 register (address 0Ah) bit description”

) and to DAC_B_GAIN_FINE[5:0]

(register 0Dh; see

Table 31 “DAC_B_CFG_2 register (address 0Dh) bit description”

)

define the fine variation of the full-scale current (see

Table 14

).

Table 14.

Default settings are shown highlighted.

DAC_GAIN_FINE[5:0]

Decimal

32

...

0

...

31

The coding of the fine gain adjustment is two’s complement.

10.10 Digital offset correction

When the DAC1008D750 analog output is DC connected to the next stage, the digital

offset correction can be used to adjust the common-mode level at the output of the DAC.

It adds an offset at the end of the digital part, just before the DAC.

The settings applied to DAC_A_OFFSET[11:0] (register 09h; see

Table 27

“DAC_A_CFG_1 register (address 09h) bit description”

and register 0Bh; see

Table 29

“DAC_A_CFG_3 register (address 0Bh) bit description”

) and to “DAC_B_OFFSET[11:0]”

I

O(fs)

coarse adjustment

I

O(fs)

(mA)

Binary

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

1.6

3.0

4.4

5.8

7.2

8.6

10.0

11.4

12.8

14.2

15.6

17.0

18.5

20.0

21.0

22.0

I

O(fs)

fine adjustment

Delta I

O(fs)

Two’s complement

10 0000

...

00 0000

...

01 1111

10 %

...

0

...

+10 %

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DAC1208D650HN | Dual 12-bit DAC; up to 650 Msps; 2×, 4× or 8× interpolating |

| DAC1208D650HN | Dual 12-bit DAC; up to 650 Msps; 2×, 4× or 8× interpolating |

| DAC1208D750HN | Dual 12-bit DAC; up to 750 Msps; 2×, 4× or 8× interpolating |

| DAC1208D750HN | Dual 12-bit DAC; up to 750 Msps; 2×, 4× or 8× interpolating |

| DL-5538S-C550-SB | 1270 nm ~ 1610 nm DFB LD MODULES 2.5 Gbps CWDM MQW-DFB LD RECEPTACLE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DAC1008D750HN/C1,5 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC DL 10BIT DAC 750MSPS 2X 4X OR 8X INT RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DAC1008LCN | 制造商:Texas Instruments 功能描述: |

| DAC1008LCN/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:10-Bit Digital-to-Analog Converter |

| DAC100ACQ3 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。