- 您現在的位置:買賣IC網 > PDF目錄67672 > GT-48207 (Galileo Technology Services, LLC) Advanced Switched Ethernet Controllers for 10+10/100 BaseX(高級交換式 10+10/100 BaseX以太網控制器) PDF資料下載

參數資料

| 型號: | GT-48207 |

| 廠商: | Galileo Technology Services, LLC |

| 英文描述: | Advanced Switched Ethernet Controllers for 10+10/100 BaseX(高級交換式 10+10/100 BaseX以太網控制器) |

| 中文描述: | 先進的交換式以太網控制器的10 10/100 BaseX(高級交換式10 10/100 BaseX以太網控制器) |

| 文件頁數: | 44/135頁 |

| 文件大小: | 1619K |

| 代理商: | GT-48207 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁

GT-482xx Switched Ethernet Controllers for 10+10/100 BaseX

GALI

LEO

TECHNOLOGY

CONFI

D

ENTI

AL

--

DO

NOT

REPRODUCE

16

Revision 1.2

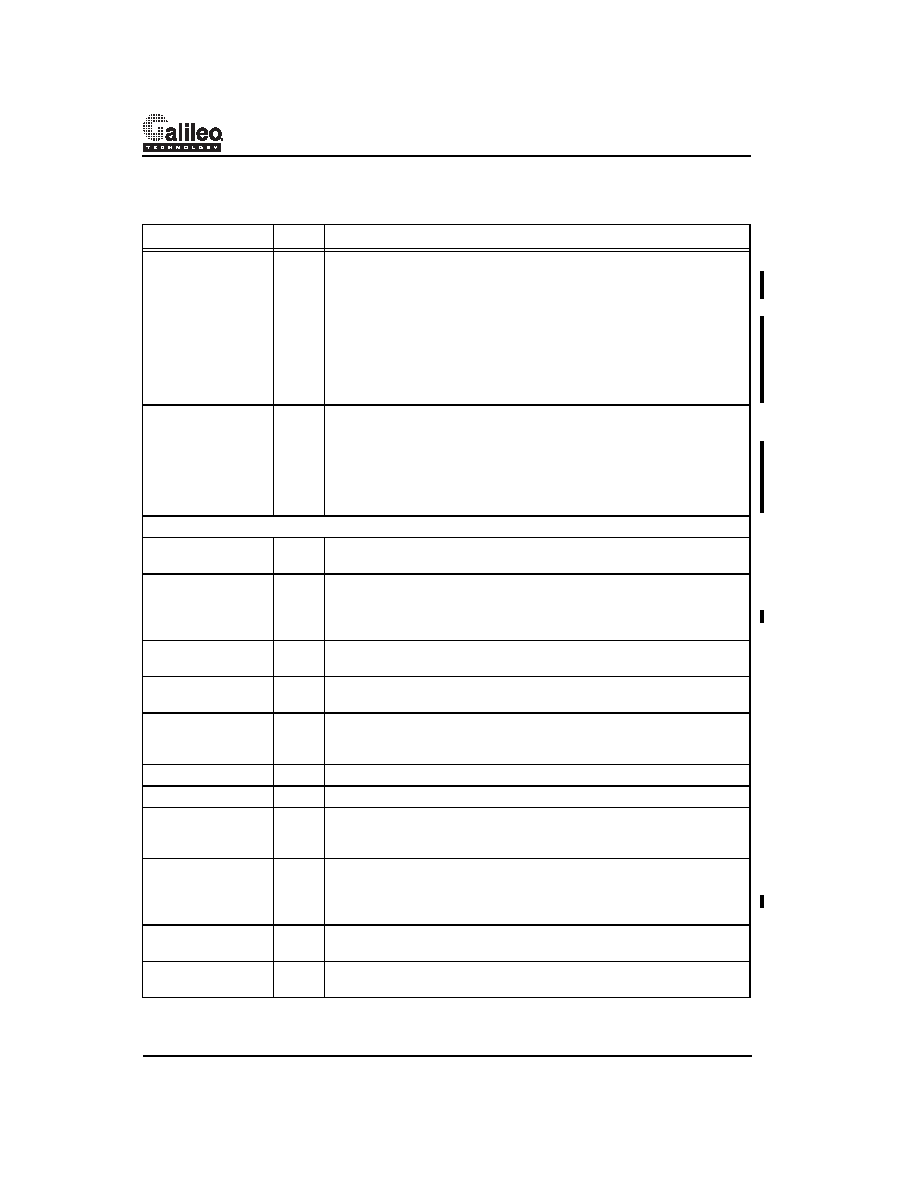

SerLinkStatus

I

Serial Link Status Indication: This pin is used to serially shift the Link Sta-

tus of ports 1 to 11 from the external PHY. LEDClk and LEDStb are used to

clock and strobe the data (assertion of LedStb indicates the beginning of the

link data stream). SerLinkStatus pin is sampled at the rising edge of LedClk.

It should be driven at the falling edge of the LEDClk.

Polarity:

High SerLinkStatus: link is good

Low SerLinkStatus: link fail.

LinkStatus[0]

I

Link Status Indication: This pin is used to indicate the Link Status of port 0

from the external PHY.

Polarity:

High LinkStatus[0]: link is good

Low LinkStatus[0]: link fail.

10/100Mbps Interface (MII)

TxEn[1:0]

O

Transmit Enable: Active HIGH. This output indicates that the packet is

being transmitted. TxEn is synchronous to TxClk.

TxClk[1:0]

I

Transmit Clock: Provides the timing reference for the transfer of TxEn, TxD

signals. TxClk frequency is one fourth of the data rate (25 MHz for 100Mbps,

2.5 MHz for 10Mbps, 60Mhz for 240Mbps). TxClk nominal frequency should

match the nominal frequency of RxClk for the same port.

TxD0[3:0]

O

Transmit Data 0: Outputs the Port0 Transmit Data. Synchronous to

TxClk[0].

TxD1[3:0]

O

Transmit Data 1: Outputs the Port1 Transmit Data. Synchronous to

TxClk[1].

Col[1:0]

I

Collision detect: Active HIGH. Indicates a collision has been detected on

the wire. This input is ignored in full-duplex mode. Col is not synchronous to

any clock.

RxD0[3:0]

I

Receive Data 0: Port 0 Receive Data. Synchronous to RxClk[0].

RxD1[3:0]

I

Receive Data 1: Port 1 Receive Data. Synchronous to RxClk[1].

RxEr[1:0]

I

Receive Error. Active HIGH. Indicates that an error was detected in the

received frame. This input is ignored when RxDV for the same port is inac-

tive.

RxClK[1:0]

I

Receive Clock. Provides the timing reference for the transfer of the

RxDV,RxD,RxEr signals (per port). Operates at either 25 MHz (100Mbps),

2.5 MHz (10Mbps) or 60Mhz (240Mbps). The nominal frequency of RxClk

(per port) should match the nominal frequency of that port’s TxClk.

RxDV[1:0]

I

Receive Data Valid: Active HIGH. Indicates that valid data is present on the

RxD lines. Synchronous to RxClk.

CrS[1:0]

I

Carrier Sense: Active HIGH. Indicates that either the transmit or receive

medium is non-idle. CrS is not synchronous to any clock.

Table 2:

Pin Functions (Continued)

Sy mbol

Ty pe

D e scr ipt io n

相關PDF資料 |

PDF描述 |

|---|---|

| GT-48208 | Advanced Switched Ethernet Controllers for 10+10/100 BaseX(高級交換式 10+10/100 BaseX以太網控制器) |

| GT-48212 | Advanced Switched Ethernet Controllers for 10+10/100 BaseX(高級交換式 10+10/100 BaseX以太網控制器) |

| GT-64010A | System Controller with PCI Interface for R4XXX/ R5000 Family CPUs(帶PCI接口用于R4XXX/ R5000 系列 CPUs的系統(tǒng)控制器) |

| GT-64012 | Secondary Cache Controller For the MIPS R4600/4650/4700/5000,(用于MIPS R4600/4650/4700/5000處理器的二級高速緩存控制器) |

| GT-64111 | System Controller for RC4640, RM523X and VR4300 CPUs(用于RC4640, RM523X和 VR4300 CPUs的系統(tǒng)控制器) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| GT48212-A6-PBB1C000 | 制造商:Marvell 功能描述: |

| GT48212-A6-PBB-C000 | 制造商:Marvell 功能描述:12 PORT E + 2 PORT FE SWITCH (MANAGED) - Trays |

| GT48300-A1-BBE1C083 | 制造商:Marvell 功能描述:Marvell GT48300-A1-BBE1C083 |

| GT48300-A1-BBE-C000 | 制造商:Marvell 功能描述:Marvell GT48300-A1-BBE-C000 |

| GT48300-A1-BBE-C08 | 制造商:Marvell 功能描述:MVLGT48300-A1-BBE-C083 4 PORT 83MHZ G.LI |

發(fā)布緊急采購,3分鐘左右您將得到回復。