- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370740 > HY5PS12823F 64Mx8|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M PDF資料下載

參數(shù)資料

| 型號: | HY5PS12823F |

| 英文描述: | 64Mx8|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| 中文描述: | 64Mx8 | 1.8 | 8K的| D43/D44/D54/D55 |的DDR II內(nèi)存- 512M |

| 文件頁數(shù): | 32/66頁 |

| 文件大?。?/td> | 862K |

| 代理商: | HY5PS12823F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

Rev. 0.52/Nov. 02 32

HY5PS12423(L)F

HY5PS12823(L)F

HY5PS121623(L)F

OCD impedance adjust(continued)

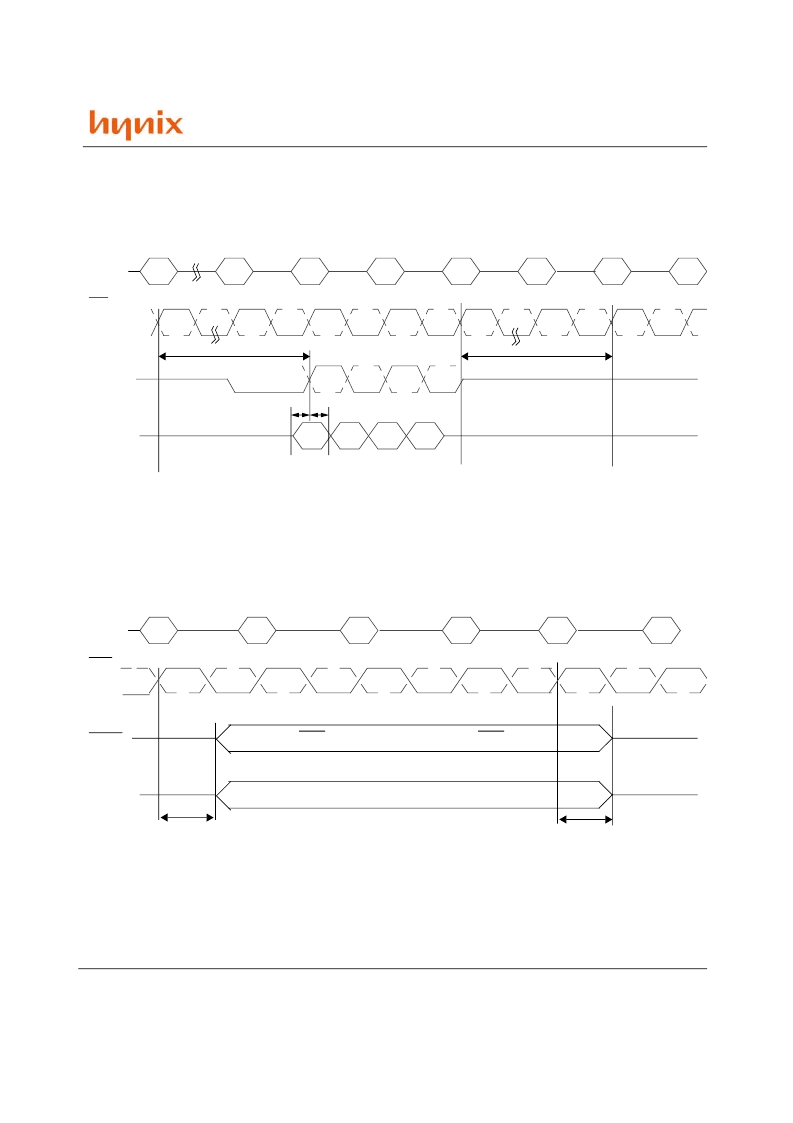

For proper operation of adjust mode, WL = RL - 1 = AL + CL -1 clocks and tDS/tDH should be met as the following tim-

ing diagram. For input data pattern for adjustment, DT0-DT3 is a fixed order and “not affected by MRS addressing

mode (ie. sequential or interleave)

Drive Mode

Drive mode, both Drive(1) and Drive(0), is used for controllers to measure DDR-II SDRAM Driver impedance before

OCD impedance adjustment. In this mode, all outputs are driven out tOIT after “enter drive mode” command and all

output drivers are turned off tOIT after “OCD calibration mode exit” command as the following timing diagram.

CMD

EMRS

NOP

NOP

NOP

NOP

NOP

EMRS

NOP

D

T0

D

T1

D

T2

D

T3

tWR

tDStDH

WL

CK

CK

DQS_in

DQ_in

OCD adjust mode

OCD calibration mode exit

CMD

tOIT(0~12ns)

CK

CK

DQS

DQS

DQ

tOIT(0~12ns)

Hi-Z

Hi-Z

DQS high & DQS low for Drive(1), DQS low & DQS high for Drive(0)

DQs high for Drive(1)

DQs low for Drive(0)

Enter Drive mode

OCD calibration mode exit

NOP

EMRS

NOP

NOP

NOP

EMRS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5PS12823LF | 64Mx8|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| HY5P | Current Transducers HY 5 to 25-P/SP1 |

| HY5R256HC | -|2.5V|8K|40|Direct RDRAM - 256M |

| HY5R288HC | -|2.5V|8K|40|Direct RDRAM - 288M |

| HY5V16CF | 1Mx16|3.3V|4K|H|SDR SDRAM - 16M |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5PS12823LF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64Mx8|1.8V|8K|D43/D44/D54/D55|DDR II SDRAM - 512M |

| HY5PS1G1631AFP | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

| HY5PS1G1631AFP-Y5 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

| HY5PS1G1631ALFP | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

| HY5PS1G1631ALFP-Y5 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。