- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377125 > ID8259A (Intel Corp.) PROGRAMMABLE INTERRUPT CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | ID8259A |

| 廠商: | Intel Corp. |

| 英文描述: | PROGRAMMABLE INTERRUPT CONTROLLER |

| 中文描述: | 可編程中斷控制器 |

| 文件頁(yè)數(shù): | 16/24頁(yè) |

| 文件大?。?/td> | 325K |

| 代理商: | ID8259A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

8259A

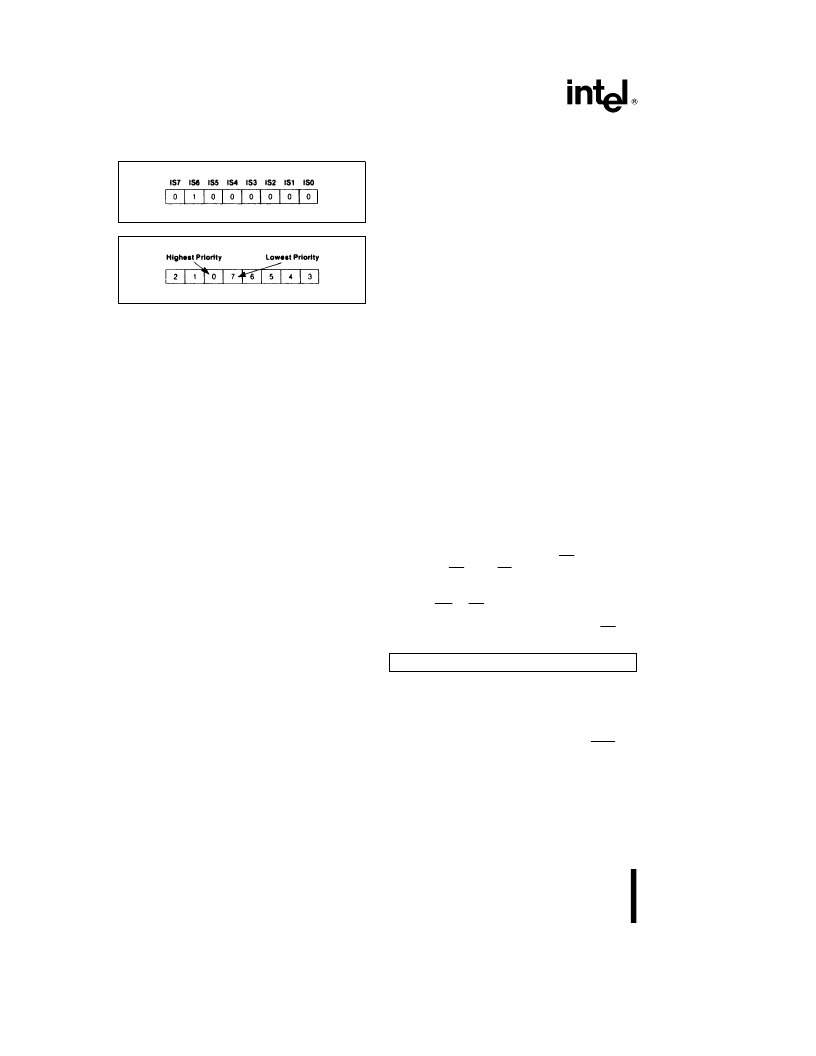

After Rotate

(IR4 was serviced, all other priorities

rotated correspondingly)

‘‘IS’’ Status

231468–20

Priority Status

231468–21

There are two ways to accomplish Automatic Rota-

tion using OCW2, the Rotation on Non-Specific EOI

Command (R

e

1, SL

e

0, EOI

e

1) and the Ro-

tate in Automatic EOI Mode which is set by (R

e

1,

SL

e

0, EOI

e

0) and cleared by (R

e

0, SL

e

0,

EOI

e

0).

Specific Rotation

(Specific Priority)

The programmer can change priorities by program-

ming the bottom priority and thus fixing all other pri-

orities; i.e., if IR5 is programmed as the bottom prior-

ity device, then IR6 will have the highest one.

The Set Priority command is issued in OCW2 where:

R

e

1, SL

e

1, L0–L2 is the binary priority level

code of the bottom priority device.

Observe that in this mode internal status is updated

by software control during OCW2. However, it is in-

dependent of the End of Interrupt (EOI) command

(also executed by OCW2). Priority changes can be

executed during an EOI command by using the Ro-

tate on Specific EOI command in OCW2 (R

e

1, SL

e

1, EOI

e

1 and LO–L2

e

IR level to receive

bottom priority).

Interrupt Masks

Each Interrupt Request input can bem masked indi-

vidually by the Interrupt Mask Register (IMR) pro-

grammed through OCW1. Each bit in the IMR masks

one interrupt channel if it is set (1). Bit 0 masks IR0,

Bit 1 masks IR1 and so forth. Masking an IR channel

does not affect the other channels operation.

Special Mask Mode

Some applications may require an interrupt service

routine to dynamically alter the system priority struc-

ture during its execution under software control. For

example, the routine may wish to inhibit lower priori-

ty requests for a portion of its execution but enable

some of them for another portion.

The difficulty here is that if an Interrupt Request is

acknowledged and an End of Interrupt command did

not reset its IS bit (i.e., while executing a service

routine), the 8259A would have inhibited all lower

priority requests with no easy way for the routine to

enable them.

That is where the Special Mask Mode comes in. In

the special Mask Mode, when a mask bit is set in

OCW1, it inhibits further interrupts at that level and

enables interrupts fromall other levels (lower as well

as higher) that are not masked.

Thus, any interrupts may be selectively enabled by

loading the mask register.

The special Mask Mode is set by OWC3 where:

SSMM

e

1, SMM

e

1, and cleared where SSMM

e

1, SMM

e

0.

Poll Command

In Poll mode the INT output functions as it normally

does. The microprocessor should ignore this output.

This can be accomplished either by not connecting

the INT output or by masking interrupts within the

microprocessor, thereby disabling its interrupt input.

Service to devices is achieved by software using a

Poll command.

The Poll command is issued by setting P

e

‘1’’ in

OCW3. The 8259A treats the next RD pulse to the

8259A (i.e., RD

e

0, CS

e

0) as an interrupt ac-

knowledge, sets the appropriate IS bit if there is a

request, and reads the priority level. Interrupt is fro-

zen from WR to RD.

The word enabled onto the data bus during RD is:

D7

D6

D5

D4

D3

D2

D1

D0

I

D

D

D

D

W2

W1

W0

W0–W2:Binary code of the highest priority level

requesting service.

I: Equal to ‘‘1’’ if there is an interrupt.

This mode is useful if there is a routine command

common to several levels so that the INTA se-

quence is not needed (saves ROM space). Another

application is to use the poll mode to expand the

number of priority levels to more than 64.

Reading the 8259A Status

The input status of several internal registers can be

read to update the user information on the system.

16

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDQS34X245 | QUICKSWITCH-R PRODUCTS HIGH-SPEED CMOS QUICKSWITCH 32-BIT MULTIWIDTH-TM BUS SWITCHES |

| IDQS34X245Q3 | QUICKSWITCH-R PRODUCTS HIGH-SPEED CMOS QUICKSWITCH 32-BIT MULTIWIDTH-TM BUS SWITCHES |

| IDQS34X245Q3G | QUICKSWITCH-R PRODUCTS HIGH-SPEED CMOS QUICKSWITCH 32-BIT MULTIWIDTH-TM BUS SWITCHES |

| IDT2305A | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT2305A-1HDCG | 3.3V ZERO DELAY CLOCK BUFFER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ID8259A-2B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Interrupt Controller |

| ID8259AB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Interrupt Controller |

| ID8259-ADFEAR | 制造商:iDESYN 功能描述:iD8259-ADFER 3A,ADJ , 2MHz, Synchronous Step-Down DC/DC Converter / |

| ID82C237 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ID82C237-12 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS High Performance Programmable DMA Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。