- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377125 > ID8259A (Intel Corp.) PROGRAMMABLE INTERRUPT CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | ID8259A |

| 廠商: | Intel Corp. |

| 英文描述: | PROGRAMMABLE INTERRUPT CONTROLLER |

| 中文描述: | 可編程中斷控制器 |

| 文件頁數(shù): | 9/24頁 |

| 文件大小: | 325K |

| 代理商: | ID8259A |

8259A

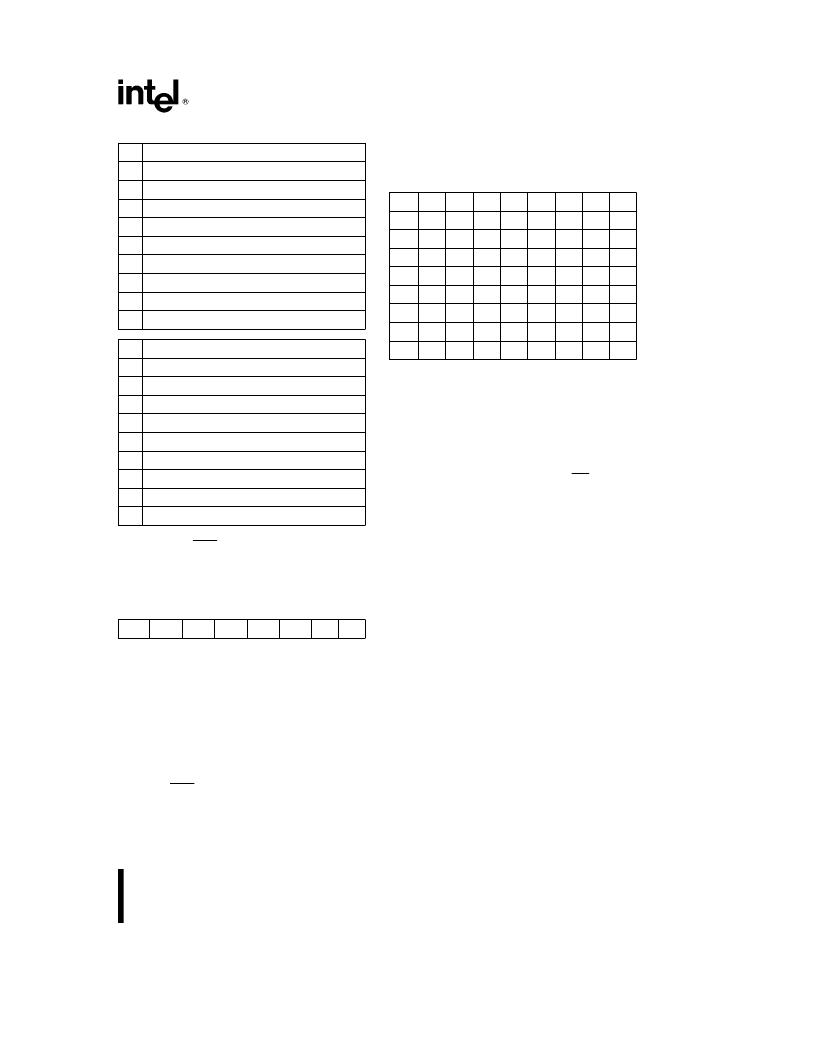

Content of Second Interrupt Vector Byte

IR

Interval

e

4

D7

D6

D5

D4

D3

D2

D1

D0

7

A7

A6

A5

1

1

1

0

0

6

A7

A6

A5

1

1

0

0

0

5

A7

A6

A5

1

0

1

0

0

4

A7

A6

A5

1

0

0

0

0

3

A7

A6

A5

0

1

1

0

0

2

A7

A6

A5

0

1

0

0

0

1

A7

A6

A5

0

0

1

0

0

0

A7

A6

A5

0

0

0

0

0

IR

Interval

e

8

D7

D6

D5

D4

D3

D2

D1

D0

7

A7

A6

1

1

1

0

0

0

6

A7

A6

1

1

0

0

0

0

5

A7

A6

1

0

1

0

0

0

4

A7

A6

1

0

0

0

0

0

3

A7

A6

0

1

1

0

0

0

2

A7

A6

0

1

0

0

0

0

1

A7

A6

0

0

1

0

0

0

0

A7

A6

0

0

0

0

0

0

During the third INTA pulse the higher address of the

appropriate service routine, which was programmed

as byte 2 of the initialization sequence (A

8

–A

15

), is

enabled onto the bus.

Content of Third Interrupt Vector Byte

D6

D5

D4

D7

D3

D2

D1

D0

A15

A14

A13

A12

A11

A10

A9

A8

8086, 8088

8086 mode is similar to MCS-80 mode except that

only two Interrupt Acknowledge cycles are issued by

the processor and no CALL opcode is sent to the

processor. The first interrupt acknowledge cycle is

similar to that of MCS-80, 85 systems in that the

8259A uses it to internally freeze the state of the

interrupts for priority resolution and as a master it

issues the interrupt code on the cascade lines at the

end of the INTA pulse. On this first cycle it does not

issue any data to the processor and leaves its data

bus buffers disabled. On the second interrupt ac-

knowledge cycle in 8086 mode the master (or slave

if so programmed) will send a byte of data to the

processor with the acknowledged interrupt code

composed as follows (note the state of the ADI

mode control is ignored and A

5

–A

11

are unused in

8086 mode):

Content of Interrupt Vector Byte

for 8086 System Mode

D7

D6

D5

D4

D3

D2

D1

D0

IR7

T7

T6

T5

T4

T3

1

1

1

IR6

T7

T6

T5

T4

T3

1

1

0

IR5

T7

T6

T5

T4

T3

1

0

1

IR4

T7

T6

T5

T4

T3

1

0

0

IR3

T7

T6

T5

T4

T3

0

1

1

IR2

T7

T6

T5

T4

T3

0

1

0

IR1

T7

T6

T5

T4

T3

0

0

1

IR0

T7

T6

T5

T4

T3

0

0

0

PROGRAMMING THE 8259A

The 8259A accepts two types of command words

generated by the CPU:

1. Initialization Command Words (ICWs): Before

normal operation can begin, each 8259A in the

system must be brought to a starting pointDby a

sequence of 2 to 4 bytes timed by WR pulses.

2. Operation Command Words (OCWs): These are

the command words which command the 8259A

to operate in various interrupt modes. These

modes are:

a. Fully nested mode

b. Rotating priority mode

c. Special mask mode

d. Polled mode

The OCWs can be written into the 8259A anytime

after initialization.

INITIALIZATION COMMAND WORDS

(ICWS)

General

Whenever a command is issued with A0

e

0 and D4

e

1, this is interpreted as Initialization Command

Word 1 (ICW1). ICW1 starts the intiitalization se-

quence during which the following automatically oc-

cur.

a. The edge sense circuit is reset, which means that

following initialization, an interrupt request (IR) in-

put must make a low-to-high transistion to gener-

ate an interrupt.

9

相關PDF資料 |

PDF描述 |

|---|---|

| IDQS34X245 | QUICKSWITCH-R PRODUCTS HIGH-SPEED CMOS QUICKSWITCH 32-BIT MULTIWIDTH-TM BUS SWITCHES |

| IDQS34X245Q3 | QUICKSWITCH-R PRODUCTS HIGH-SPEED CMOS QUICKSWITCH 32-BIT MULTIWIDTH-TM BUS SWITCHES |

| IDQS34X245Q3G | QUICKSWITCH-R PRODUCTS HIGH-SPEED CMOS QUICKSWITCH 32-BIT MULTIWIDTH-TM BUS SWITCHES |

| IDT2305A | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT2305A-1HDCG | 3.3V ZERO DELAY CLOCK BUFFER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ID8259A-2B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Interrupt Controller |

| ID8259AB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Interrupt Controller |

| ID8259-ADFEAR | 制造商:iDESYN 功能描述:iD8259-ADFER 3A,ADJ , 2MHz, Synchronous Step-Down DC/DC Converter / |

| ID82C237 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ID82C237-12 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS High Performance Programmable DMA Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復。