- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67716 > IDT79R4700-100G (INTEGRATED DEVICE TECHNOLOGY INC) 64-BIT, 100 MHz, RISC PROCESSOR, CPGA179 PDF資料下載

參數(shù)資料

| 型號: | IDT79R4700-100G |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 100 MHz, RISC PROCESSOR, CPGA179 |

| 封裝: | PGA-179 |

| 文件頁數(shù): | 19/25頁 |

| 文件大?。?/td> | 437K |

| 代理商: | IDT79R4700-100G |

IDT79R4700/RV4700

COMMERCIAL TEMPERATURE RANGE

3

HARDWARE OVERVIEW

The R4700 processor family brings a high-level of inte-

gration designed for high-performance computing. The

R4700’s key elements are briefly described below. A more

detailed explanation of each subsystem is available in the

user’s manual.

Pipeline

The R4700 uses a simple 5-stage pipeline, similar to

the pipeline structure implemented in the IDT79R3000.

This pipeline’s simplicity allows the R4700 to be lower cost

and lower power than super-scalar or super-pipelined

processors. However, unlike the R3000, the R4700 does

virtual-to-physical translation in parallel with cache access.

This capability allows the R4700 to operate at over three

times the frequency of the R30xx and to support a larger

TLB for address translation. The pipeline stages are shown

Integer Execution Engine

The R4700 implements the MIPS-III Instruction Set

architecture and is upwardly compatible with applications

that run on earlier generation parts.

Implementation of the MIPS-III architecture results in

64-bit operations, better code density, greater multi-

processing support, improved performance for commonly

used code sequences in operating system kernels and

faster execution of floating-point intensive applications. All

resource dependencies are made transparent to the

programmer, insuring transportability among implementa-

tions of the MIPS instruction set architecture.

The MIPS integer unit implements a load/store archi-

tecture with single cycle ALU operations (logical, shift, add,

sub) and an autonomous multiply/divide unit. Register

resources include:

32 general-purpose orthogonal integer registers

HI/LO result registers, for the integer multiply/divide unit

Program counter

Also, the on-chip floating-point co-processor adds 32

floating-point registers and a floating-point control/status

register.

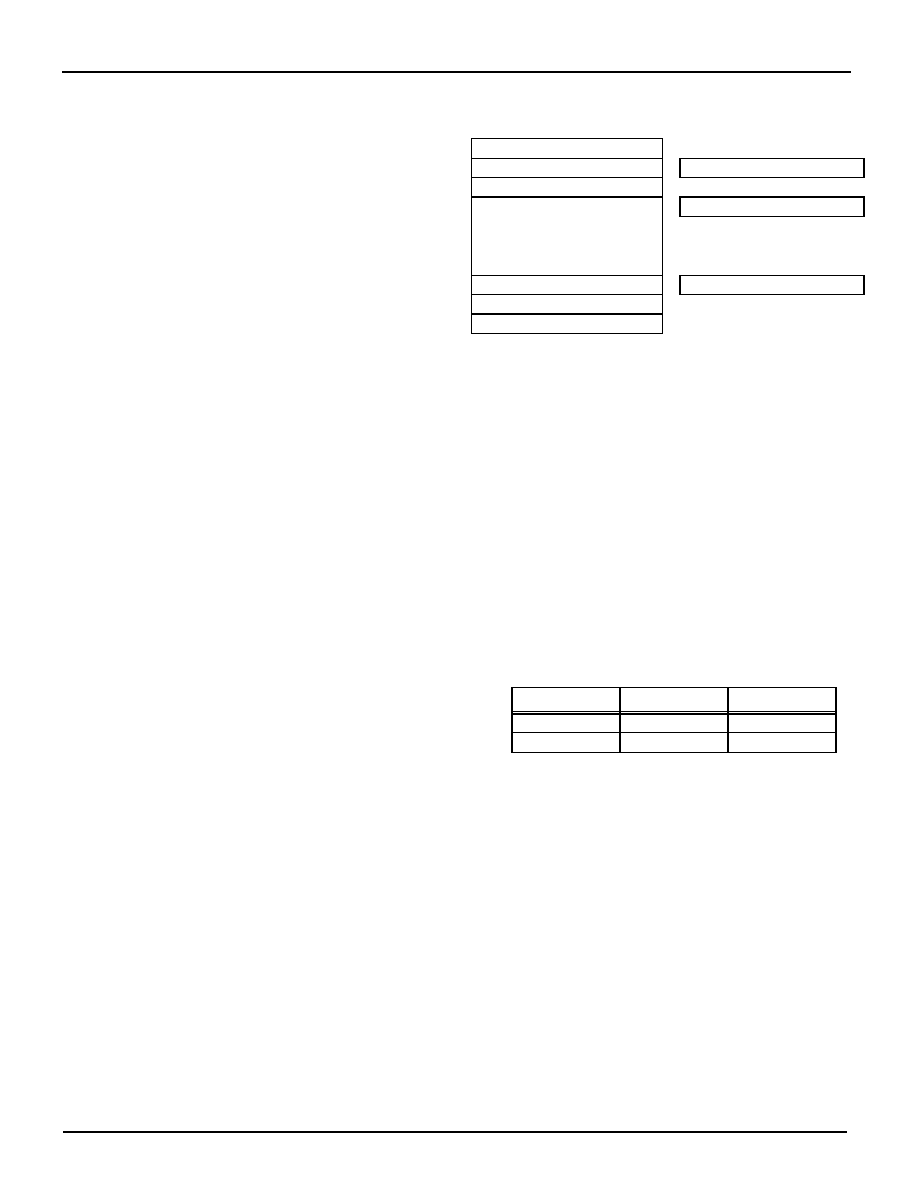

Register File

The R4700 has 32 general-purpose registers (shown in

Figure 2 ). These registers are used for scalar integer oper-

ations and address calculation. The register file consists of

two read ports and one write port and is fully bypassed to

minimize operation latency in the pipeline.

ALU

The R4700 ALU consists of the integer adder and logic

unit. The adder performs address calculations in addition to

arithmetic operations, and the logic unit performs all logical

and shift operations. Each of these units is highly optimized

and can perform an operation in a single pipeline cycle.

Integer Multiply/Divide

To perform integer multiply and divide operations, the

R4700 uses the floating-point unit. The results of the opera-

tion are placed in the

HI and LO registers. The values can

then be transferred to the general purpose register file

using the MFHI/MFLO instructions. To prevent the occur-

rence of an interlock or stall, a required number (shown in

Table 1) of processor internal cycles must occur between

an integer multiply or divide and a subsequent MFHI or

MFLO operation.

Floating-Point Co-Processor

The R4700 incorporates a complete floating-point co-

processor on chip and includes a floating-point register file

and execution units. The floating-point co-processor forms

a “seamless” interface with the integer unit, decoding and

executing instructions in parallel with the integer unit.

Floating-Point Units

The R4700 floating-point execution units support single

and double precision arithmetic, as specified in the IEEE

Standard 754. The execution unit is separated into a mul-

tiply unit and a combined add/convert/divide/square root

unit. Overlap of multiplies and add/subtract is supported.

The multiplier is partially pipelined, allowing a new multiply

to begin every four cycles.

General Purpose Registers

Multiply/Divide Registers

63

0

063

0

r1

HI

r2

63

0

LO

Program Counter

63

0

r29

PC

r30

r31

Figure 2. R4700 CPU Registers

Operation

32-bit

64-bit

MULT

6 - 9

7 - 10

DIV

42

74

Table 1. Integer Multiply/Divide Cycles

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT79RV4700-80G | 64-BIT, 80 MHz, RISC PROCESSOR, CPGA179 |

| IDT79RV4700-80MS | 64-BIT, 80 MHz, RISC PROCESSOR, PQFP208 |

| IDT79RV4700200DPG | 64-BIT, 200 MHz, RISC PROCESSOR, PQFP208 |

| IDT82V3155PVG8 | PLL BASED CLOCK DRIVER, 7 TRUE OUTPUT(S), 5 INVERTED OUTPUT(S), PDSO56 |

| IDT85304-01PGGI8 | 85304 SERIES, LOW SKEW CLOCK DRIVER, 5 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT79R4700-133DP | 功能描述:IC MPU 64BIT 5V 133MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79R4700-133G | 功能描述:IC MPU 64BIT 5V 133MHZ 179-PGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| IDT79RC32H434-266BC | 功能描述:IC MPU 32BIT CORE 266MHZ 256-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Interprise™ 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點:- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| IDT79RC32H434-266BCG | 功能描述:IC MPU 32BIT CORE 266MHZ 256-BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Interprise™ 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點:- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| IDT79RC32H434-266BCGI | 功能描述:IC MPU 32BIT CORE 266MHZ 256-BGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:Interprise™ 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點:- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。