- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373157 > KM44S4020CT (SAMSUNG SEMICONDUCTOR CO. LTD.) 2M x 4Bit x 2 Banks Synchronous DRAM(2M x 4位 x 2組同步動態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號: | KM44S4020CT |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 2M x 4Bit x 2 Banks Synchronous DRAM(2M x 4位 x 2組同步動態(tài)RAM) |

| 中文描述: | 2米x 4位× 2銀行同步DRAM(2米× 4位× 2組同步動態(tài)RAM)的 |

| 文件頁數(shù): | 3/44頁 |

| 文件大小: | 604K |

| 代理商: | KM44S4020CT |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

KM44S4020C

REV. 5 Feb. '98

CMOS SDRAM

V

DD

N.C

V

SSQ

DQ0

V

DDQ

N.C

V

SSQ

DQ1

V

DDQ

N.C

N.C

WE

CAS

RAS

CS

BA

A10/AP

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

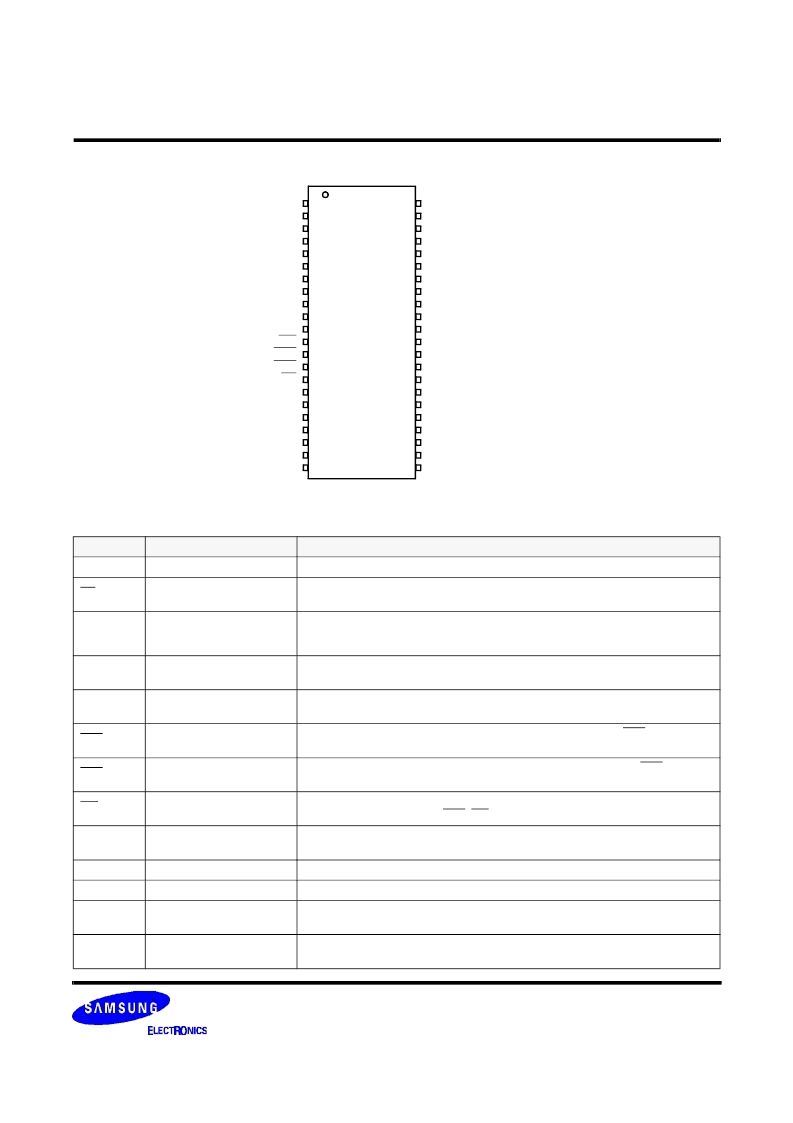

PIN CONFIGURATION

(Top view)

V

SS

N.C

V

SSQ

DQ3

V

DDQ

N.C

V

SSQ

DQ2

V

DDQ

N.C/RFU

N.C

DQM

CLK

CKE

N.C

A9

A8

A7

A6

A5

A4

V

SS

44Pin TSOP (II)

(400mil x 725mil)

(0.8 mm Pin pitch)

PIN FUNCTION DESCRIPTION

Pin

Name

Input Function

CLK

System clock

Active on the positive going edge to sample all inputs.

CS

Chip select

Disables or enables device operation by masking or enabling all inputs except

CLK, CKE and DQM

CKE

Clock enable

Masks system clock to freeze operation from the next clock cycle.

CKE should be enabled at least one cycle prior to new command.

Disable input buffers for power down in standby.

A

0

~ A

10

/AP

Address

Row/column addresses are multiplexed on the same pins.

Row address : RA

0

~ RA

10

, Column address : CA

0

~ CA

9

BA

Bank select address

Selects bank to be activated during row address latch time.

Selects bank for read/write during column address latch time.

RAS

Row address strobe

Latches row addresses on the positive going edge of the CLK with RAS low.

Enables row access & precharge.

CAS

Column address strobe

Latches column addresses on the positive going edge of the CLK with CAS low.

Enables column access.

WE

Write enable

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

DQM

Data input/output mask

Makes data output Hi-Z, t

SHZ

after the clock and masks the output.

Blocks data input when DQM active.

DQ

0

~

3

Data input/output

Data inputs/outputs are multiplexed on the same pins.

V

DD

/V

SS

Power supply/ground

Power and ground for the input buffers and the core logic.

V

DDQ

/V

SSQ

Data output power/ground

Isolated power supply and ground for the output buffers to provide improved noise

immunity.

N.C/RFU

No connection

/reserved for future use

This pin is recommended to be left No Connection on the device.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KM44S64230A | 16M x 4Bit x 4 Banks Synchronous DRAM(16M x 4位 x 4組同步動態(tài)RAM) |

| KM44V1000D | 1M x 4Bit CMOS Dynamic RAM with Fast Page Mode(1M x 4位CMOS 動態(tài)RAM(帶快速頁模式)) |

| KM44V16000B | 16M x 4Bit CMOS Dynamic RAM with Fast Page Mode(16M x 4位CMOS 動態(tài)RAM(帶快速頁模式)) |

| KM44V16100B | 16M x 4Bit CMOS Dynamic RAM with Fast Page Mode(16M x 4位CMOS 動態(tài)RAM(帶快速頁模式)) |

| KM44V16100C | 16M x 4Bit CMOS Dynamic RAM with Fast Page Mode(16M x 4位CMOS 動態(tài)RAM(帶快速頁模式)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KM44S4020CT-G10 | 制造商:SEC 功能描述:SDRAM, 4M x 4, 44 Pin, Plastic, TSOP |

| KM44V1000D | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:1M x 4Bit CMOS Dynamic RAM with Fast Page Mode |

| KM44V4000AS-6 | 制造商:Samsung Electro-Mechanics 功能描述:Dynamic RAM, Fast Page, 4M x 4, 26 Pin, Plastic, TSOP |

| KM44V4000C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 4Bit CMOS Dynamic RAM with Fast Page Mode |

| KM44V4100AT-7 | 制造商:Samsung Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。