- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377835 > M7040N-100ZA1T (意法半導(dǎo)體) 64K x 72-bit Entry NETWORK PACKET SEARCH ENGINE PDF資料下載

參數(shù)資料

| 型號: | M7040N-100ZA1T |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 64K x 72-bit Entry NETWORK PACKET SEARCH ENGINE |

| 中文描述: | 64K的× 72位的網(wǎng)絡(luò)數(shù)據(jù)包進(jìn)入搜索引擎 |

| 文件頁數(shù): | 101/159頁 |

| 文件大?。?/td> | 1088K |

| 代理商: | M7040N-100ZA1T |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁當(dāng)前第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁

101/159

M7040N

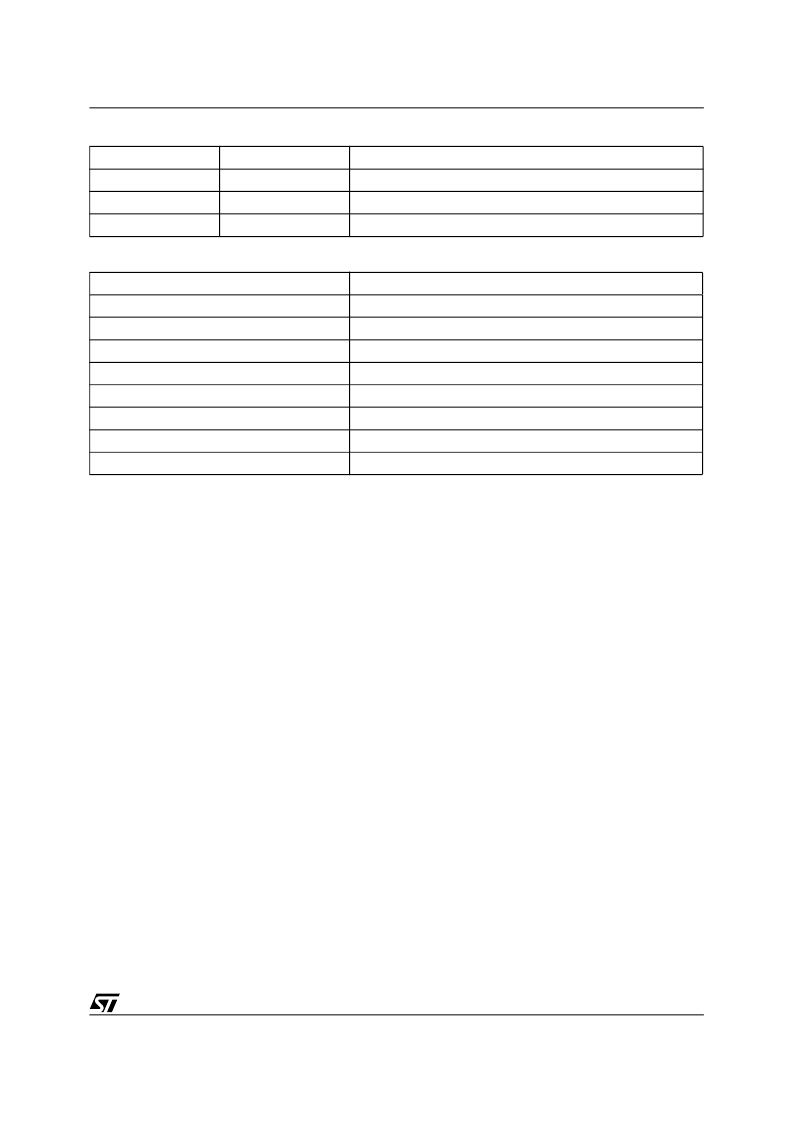

Table 45. Latency of SEARCH from Cycles C and D to SRAM Access Cycle, 288-bit

Table 46. Shift of SSF and SSV from SADR

288-bit Search on Tables Configured as x288 Using Up to 31 M7040N Devices

The hardware diagram of the search subsystem of

31 devices is shown in Figure 74, page 103. Each

of the four blocks in the diagram represents a

block of eight M7040N devices, except the last

which has seven devices.The diagram for a block

of eight devices is shown in Figure 75, page 104.

The following are the parameters programmed

into the 31 devices.

–

First thirty devices (devices 0

–

29):

CFG = 1010101010101010, TLSZ = 10,

HLAT = 000, LRAM = 0, and LDEV = 0.

–

Thirty-first device (device 30):

CFG = 1010101010101010, TLSZ = 10,

HLAT = 000, LRAM = 1, and LDEV = 1.

Note:

All 31 devices must be programmed with the

same value of TLSZ and HLAT. Only the last de-

vice in the table must be programmed with

LRAM = 1 and LDEV = 1 (Device 30 in this case).

All other upstream devices must be programmed

with LRAM = 0 and LDEV = 0 (Devices 0 through

29 in this case).

The timing diagrams referred to in this paragraph

reference the HIT/MISS assumptions defined in

Table 47, page 103. For the purpose of illustrating

the timings, it is further assumed that there is only

one device with the matching entry in each block.

Figure 77, page 106 shows the timing diagram for

a SEARCH command in the 288-bit-configured ta-

ble consisting of 31 devices for each of the eight

devices in Block 0. Figure 78, page 107 shows the

timing diagram for a SEARCH command in the

288-bit-configured table of 31 devices for all devic-

es above the winning device in Block 1. Figure 79,

page 108 shows the timing diagram for the global-

ly winning device (the final winner within its own

and all blocks) in Block 1. Figure 80, page 109

shows the timing diagram for all the devices below

the globally winning device in Block 1. Figure 81,

page 110, Figure 82, page 111, and Figure 83,

page 112, respectively, show the timing diagrams

of the devices above the globally winning device,

the globally winning device, and the devices below

the globally winning device for Block 2. Figure 84,

page 113, Figure 85, page 114, Figure 86, page

115, and Figure 87, page 116, respectively, show

the timing diagrams of the device above the glo-

bally winning device, the globally winning device,

the devices below the globally winning device (ex-

cept Device 30), and last device (Device 30) for

Block 3.

# of devices

Max Table Size

Latency in CLK Cycles

1 (TLSZ = 00)

16K x 288-bit

4

1

–

8 (TLSZ = 01)

128K x 288-bit

5

1

–

31 (TLSZ = 10)

496K x 288-bit

6

HLAT

Number of CLK Cycles

000

0

001

1

010

2

011

3

100

4

101

5

110

6

111

7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M708 | PCM REMOTE CONTROL TRANSMITTER |

| M708A | PCM REMOTE CONTROL TRANSMITTER |

| M708B1 | PCM REMOTE CONTROL TRANSMITTER |

| M708AB1 | PCM REMOTE CONTROL TRANSMITTER |

| M709 | PCM REMOTE CONTROLL TRANSMITTERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M7041 | 制造商:Tamura Corporation of America 功能描述: |

| M7045 | 制造商:Tamura Corporation of America 功能描述: |

| M705-5090142 | 功能描述:直流電源連接器 FEMALE STEREO JACK RoHS:否 制造商:Kycon 產(chǎn)品:Receptacles 觸點(diǎn)內(nèi)徑: 觸點(diǎn)外徑: 中心腳長度: 電流額定值:7.5 A 電壓額定值:20 V 安裝角:Right 安裝風(fēng)格:Cable |

| M705-5090242 | 功能描述:RCA Phono連接器 FEMALE STEREO JACK RoHS:否 制造商:Neutrik 型式:Male 端接類型:Solder 安裝風(fēng)格:Cable 方向:Horizontal |

| M705-510046 | 功能描述:RCA Phono連接器 DC JACKS RoHS:否 制造商:Neutrik 型式:Male 端接類型:Solder 安裝風(fēng)格:Cable 方向:Horizontal |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。