- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8256TVT800B (FREESCALE SEMICONDUCTOR INC) 0-BIT, OTHER DSP, PBGA783 PDF資料下載

參數(shù)資料

| 型號: | MSC8256TVT800B |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 0-BIT, OTHER DSP, PBGA783 |

| 封裝: | 29 X 29 MM, LEAD FREE, PLASTIC, FCBGA-783 |

| 文件頁數(shù): | 35/68頁 |

| 文件大小: | 910K |

| 代理商: | MSC8256TVT800B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

MSC8256 Six-Core Digital Signal Processor Data Sheet, Rev. 3

Electrical Characteristics

Freescale Semiconductor

40

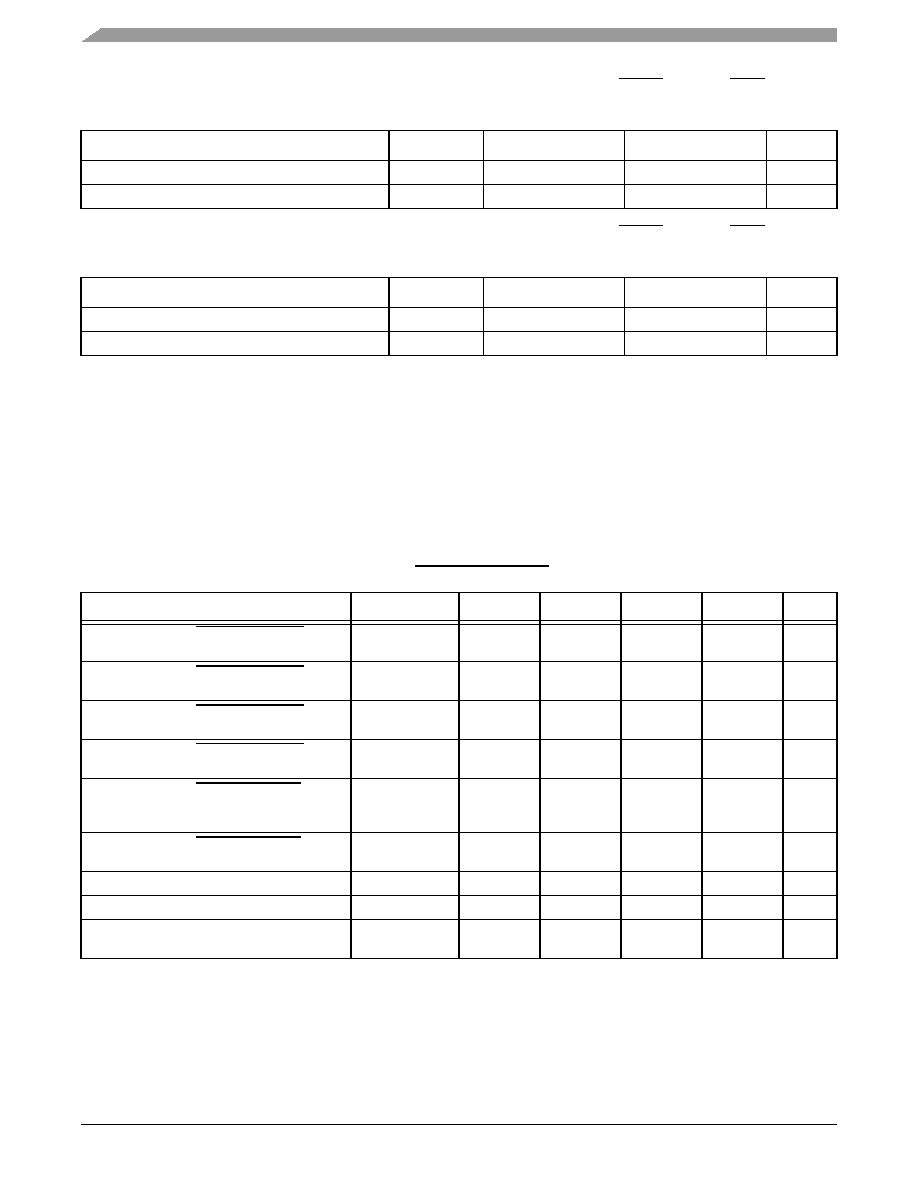

Table 22 provides the DDR2 differential specifications for the differential signals MDQS/MDQS and MCK/MCK.

Table 23 provides the DDR3 differential specifications for the differential signals MDQS/MDQS and MCK/MCK.

2.6.2

HSSI AC Timing Specifications

The following subsections define the AC timing requirements for the SerDes reference clocks, the PCI Express data lines, the

Serial RapidIO data lines, and the SGMII data lines.

2.6.2.1

AC Requirements for SerDes Reference Clock

Table 24 lists AC requirements for the SerDes reference clocks.

Note:

Specifications are valid at the recommended operating conditions listed in Table 3.

Table 22. DDR2 SDRAM Differential Electrical Characteristics

Parameter

Symbol

Min

Max

Unit

Input AC differential cross-point voltage

VIXAC

0.5

× GVDD – 0.175

0.5

× GVDD + 0.175

V

Output AC differential cross-point voltage

VOXAC

0.5

× GVDD – 0.125

0.5

× GVDD + 0.125

V

Table 23. DDR3 SDRAM Differential Electrical Characteristics

Parameter

Symbol

Min

Max

Unit

Input AC differential cross-point voltage

VIXAC

0.5

× GVDD – 0.150

0.5

× GVDD + 0.150

V

Output AC differential cross-point voltage

VOXAC

0.5

× GVDD – 0.115

0.5

× GVDD + 0.115

V

Table 24. SR[1–2]_REF_CLK and SR[1–2]_REF_CLK Input Clock Requirements

Parameter

Symbol

Min

Typical

Max

Units

Notes

SR[1–2]_REF_CLK/SR[1–2]_REF_CLK

frequency range

tCLK_REF

—

100/125

—

MHz

1

SR[1–2]_REF_CLK/SR[1–2]_REF_CLK clock

frequency tolerance

tCLK_TOL

–350

—

350

ppm

—

SR[1–2]_REF_CLK/SR[1–2]_REF_CLK

reference clock duty cycle (measured at 1.6 V)

tCLK_DUTY

40

50

60

%

—

SR[1–2]_REF_CLK/SR[1–2]_REF_CLK max

deterministic peak-peak jitter at 10-6 BER

tCLK_DJ

——

42

ps

—

SR[1–2]_REF_CLK/SR[1–2]_REF_CLK total

reference clock jitter at 10-6 BER (peak-to-peak

jitter at ref_clk input)

tCLK_TJ

——

86

ps

2

SR[1–2]_REF_CLK/SR[1–2]_REF_CLK

rising/falling edge rate

tCLKRR/tCLKFR

1—4

V/ns

3

Differential input high voltage

VIH

200

—

mV

4

Differential input low voltage

VIL

—

–200

mV

4

Rising edge rate (SR[1–2]_REF_CLK) to falling

edge rate (SR[1–2]_REF_CLK) matching

Rise-Fall

Matching

——

20

%

5, 6

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8256SVT1000B | 0-BIT, OTHER DSP, PBGA783 |

| MSM5547RS | 0 TIMER(S), REAL TIME CLOCK, PDIP42 |

| MSM58321RS | 0 TIMER(S), REAL TIME CLOCK, PDIP16 |

| MSM6052GS | 4-BIT, MROM, MICROCONTROLLER, PQFP44 |

| MSM6242BGS | 1 TIMER(S), REAL TIME CLOCK, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC83301 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS GENERAL PURPOSE AMPLIFIER APPLICATIONS |

| MSC83303 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS GENERAL PURPOSE AMPLIFIER APPLICATIONS |

| MSC83305 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:RF & MICROWAVE TRANSISTORS GENERAL PURPOSE AMPLIFIER APPLICATIONS |

| MSC85623 | 制造商:ASI 制造商全稱:ASI 功能描述:NPN RF TRANSISTOR |

| MSC8W38T15-L6 | 功能描述:電纜束帶 MS Strapping, 316 SS, Nylon FC, .38" (9. RoHS:否 制造商:Phoenix Contact 產(chǎn)品:Cable Tie Mounts 類型:Adhesive 顏色:Black 材料:Acrylonitrile Butadiene Styrene (ABS) 長度:19 mm 寬度:19 mm 抗拉強度: |

發(fā)布緊急采購,3分鐘左右您將得到回復。