- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT90870 (Zarlink Semiconductor Inc.) Flexible 12 k Digital Switch (F12kDX) PDF資料下載

參數(shù)資料

| 型號: | MT90870 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | Flexible 12 k Digital Switch (F12kDX) |

| 中文描述: | 靈活的12畝數(shù)字交換機(jī)(F12kDX) |

| 文件頁數(shù): | 15/86頁 |

| 文件大?。?/td> | 2093K |

| 代理商: | MT90870 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

MT90870

Data Sheet

15

Zarlink Semiconductor Inc.

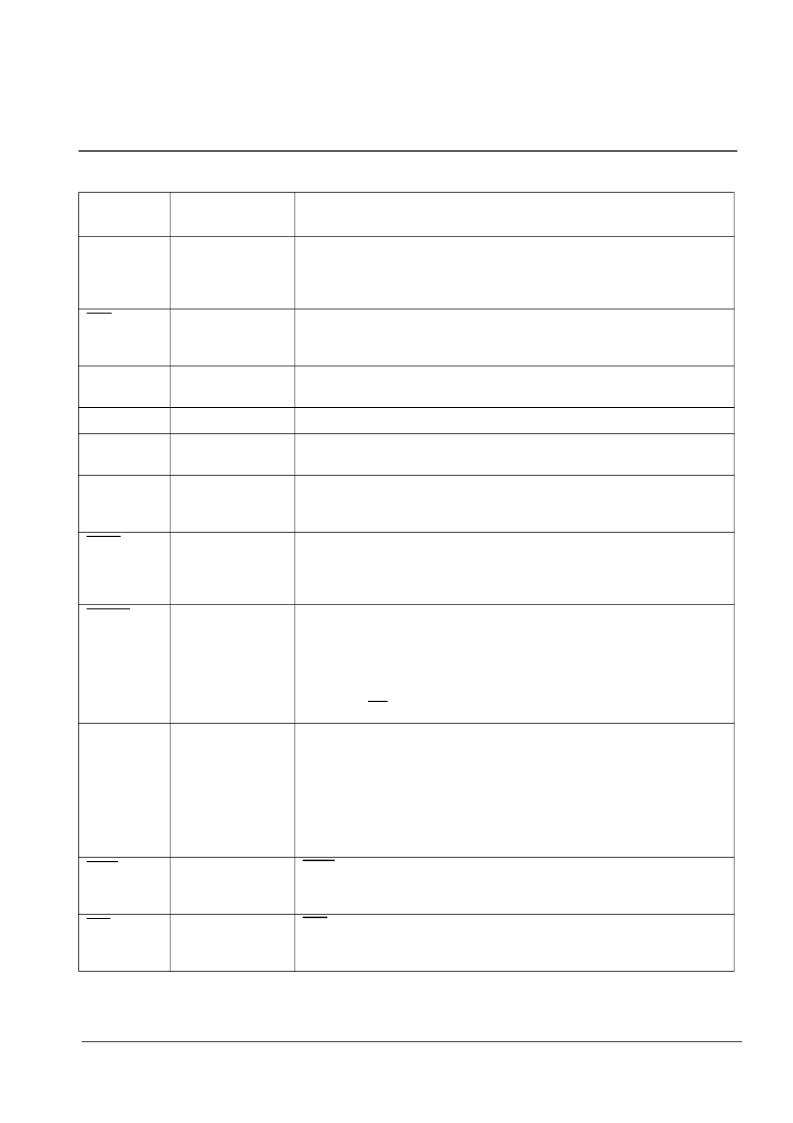

D0 - D15

V10, Y9, W9, V9,

U9, Y8, W8, V8,

W7, V7, U7, Y6,

W6, V6, Y5, W5

Data Bus 0 - 15 (5 V Tolerant).

These pins form the 16-bit data bus of the

microprocessor port. (Data D0 = LSB).

DTA

A13

Data Transfer Acknowledgment (5 V Tolerant).

This active low output

indicates that a data bus transfer is complete. A pull-up resistor is

required to hold a HIGH level. (Max. I

OL

= 10mA).

TMS

D12

Test Mode Select (5 V Tolerant with internal pull-up).

JTAG signal that

controls the state transitions of the TAP controller.

TCK

A14

Test Clock (5 V Tolerant).

Provides the clock to the JTAG test logic.

TDi

B13

Test Serial Data In (5 V Tolerant with internal pull-up).

JTAG serial test

instructions and data are shifted in on this pin.

TDo

C13

Test Serial Data Out (5 V Tolerant Three-state Output).

JTAG serial

data is output on this pin on the falling edge of TCK. This pin is held in

high impedance state when JTAG is not enabled.

TRST

B14

Test Reset (5 V Tolerant with internal pull-up)

Asynchronously

initializes the JTAG TAP controller to the Test-Logic-Reset state. To be

pulsed low during power-up for JTAG testing. This pin must be held LOW

for normal functional operation of the device.

RESET

C12

Device Reset (5 V Tolerant with internal pull-up).

This input (active

LOW) asynchronously applies reset and synchronously releases reset to

the device. In the reset state, the outputs LSTo0 - 15 and BSTo0 - 31 are

set to a high or high impedance depending on the state of the LORS and

BORS external control pins, respectively. It clears the device registers

and internal counters. This pin must stay low for more than 2 cycles of

input clock C8i for the reset to be invoked.

LSTi0-15

L18, L19, L20,

M17, M18,

M19, M20, N18,

N19, N20, P17,

P19, P20, R18,

R19, R20,

Local Serial Input Streams 0 to 15 (5 V Tolerant with internal pull-

down).

These pins accept serial TDM data streams at a data-rate of:

16.384 Mb/s (with 256 channels per stream),

8.192 Mb/s (with 128 channels per stream),

4.096 Mb/s (with 64 channels per stream), or

2.048 Mb/s (with 32 channels per stream).

The data-rate is independently programmable for each input stream.

C16o

W13

C16o Output Clock (Three-state Output).

A 16.384 MHz clock output.

The clock falling edge or rising edge is aligned with the Local frame

boundary, this is controlled by the COPOL bit of the Control Register.

C8o

V13

C8o Output Clock (Three-state Output).

A 8.192 MHz clock output. The

clock falling edge or rising edge is aligned with the Local frame boundary,

this is controlled by the COPOL bit of the Control Register.

Pin Description (continued)

Name

Package

Coordinates

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT90871AV | Flexible 8K Digital Switch (F8KDX) |

| MT90871 | Flexible 8K Digital Switch (F8KDX) |

| MT90883 | TDM to Packet Processors |

| MT91600 | Programmable SLIC |

| MT91600AN | Programmable SLIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT90870AG | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 12K X 12K/8K X 4K 1.8V/3.3V 272BGA - Trays |

| MT90870AG2 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 12K X 12K/8K X 4K 1.8V/3.3V 272BGA - Trays |

| MT90871 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Flexible 8K Digital Switch (F8KDX) |

| MT90871AV | 制造商:Microsemi Corporation 功能描述:FLEXIBLE 8K DIGITAL SWITCH 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC DGTL SWITCH F8KDX 196PBGA 制造商:Microsemi Corporation 功能描述:IC DGTL SWITCH F8KDX 196PBGA |

| MT90871AV2 | 制造商:Microsemi Corporation 功能描述:PB FREE FLEXIBLE 8K DIGITAL SWITCH - Bulk 制造商:Microsemi Corporation 功能描述:IC, TDM SWITCH 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC DGTL SWITCH F8KDX 196PBGA 制造商:Microsemi Corporation 功能描述:IC DGTL SWITCH F8KDX 196PBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。