- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98293 > TS83102G0BMGS (ATMEL CORP) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 PDF資料下載

參數(shù)資料

| 型號: | TS83102G0BMGS |

| 廠商: | ATMEL CORP |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| 封裝: | HERMATIC, CI-CGA-152 |

| 文件頁數(shù): | 23/52頁 |

| 文件大?。?/td> | 1548K |

| 代理商: | TS83102G0BMGS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

3

5360A–BDC–06/05

TS83102G0BMGS

3.

Specification

Note:

Absolute maximum ratings are short term limiting values (referenced to GND = 0V), to be applied individually, while other

parameters are within specified operating conditions. Long exposure to maximum ratings may affect device reliability. All inte-

grated circuits have to be handled with appropriate care to avoid damage due to ESD. Damage caused by inappropriate

handling or storage could range from performance degradation to complete failure.

3.1

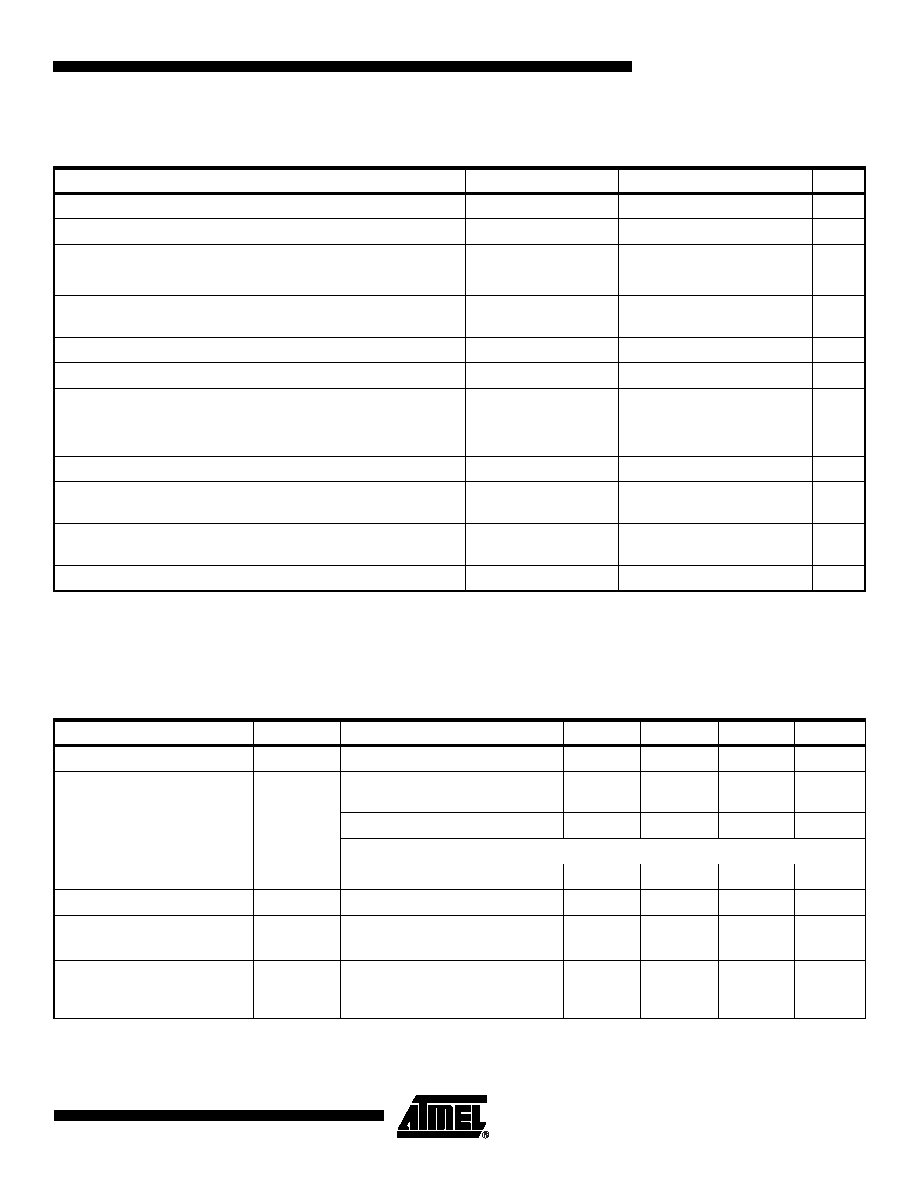

Absolute Maximum Ratings

Parameter

Symbol

Comments

Value

Unit

Positive supply voltage

VCC

GND to 6.0

V

Digital negative supply voltage

D

VEE

GND to -5.7

V

Digital positive supply voltage

VPLUSD

GND - 1.1 to 2.5

V

Negative supply voltage

VEE

GND to -5.5

V

Maximum difference between negative

supply voltages

DVEE to VEE

0.3

V

Analog input voltages

VIN or VINB

-1.5 to 1.5

V

Maximum difference between VIN and VINB

V

IN - VINB

-1.5 to 1.5

V

Clock input voltage

VCLK or VCLKB

-1 to 1

V

Maximum difference between VCLK and

VCLKB

VCLK - VCLKB

-1 to 1

Vpp

Static input voltage

VD

GA, SDA

-5 to 0.8

V

Digital input voltage

VD

SDAEN, DRRB, B/GB,

PGEB, DECB

-5 to 0.8

V

Digital output voltage

V

O

VPLUSD min operating -2.2 to

VPLUSD max operating + 0.8

V

Junction temperature

T

J

130

°C

3.2

Recommended Conditions of Use

Parameter

Symbol

Comments

Min

Typ

Max

Unit

Positive supply voltage

V

CC

4.7555.25

V

Positive digital supply voltage

V

PLUSD

Differential ECL output

compatibility

- 0.9

- 0.8

- 0.7

V

LVDS output compatibility

1.375

1.45

1.525

V

Grounded(1)

Maximum operating VPLUSD

1.7

V

Negative supply voltages

V

EE, DVEE

- 5.25

- 5.0

- 4.75

V

Differential analog input

voltage (full-scale)

VIN, VINB

V

IN - VINB

50

differential or single-ended

±113

450

±125

500

±137

550

mV

mVpp

Clock input power level

(ground common mode)

P

CLK, PCLKB

50

single-ended clock input or

100

differential clock

(recommended)

- 4

0

4

dBm

相關PDF資料 |

PDF描述 |

|---|---|

| TS83102G0BVGL | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| TS83102G0BCGL | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| TS83110CZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110VZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TS83102G0BVGL | 制造商:e2v technologies 功能描述:ADC SGL 2GSPS 10-BIT PARALLEL 152CBGA - Trays |

| TS83102G0CGL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog to Digital Converter |

| TS83102G0GSZR5 | 制造商:e2v technologies 功能描述:TS83102G0GSZR5 - Trays |

| TS831-3I | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MICROPOWER VOLTAGE SUPERVISOR RESET ACTIVE LOW |

| TS831-3ID | 功能描述:監(jiān)控電路 2.71V Micropower AL RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復位:Resettable 監(jiān)視器:No Watchdog 電池備用開關:No Backup 上電復位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。