- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359438 > VT6305 (Electronic Theatre Controls, Inc.) PCI 1394 Host Controller PDF資料下載

參數(shù)資料

| 型號(hào): | VT6305 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | PCI 1394 Host Controller |

| 中文描述: | 1394主控制器的PCI |

| 文件頁(yè)數(shù): | 14/35頁(yè) |

| 文件大?。?/td> | 220K |

| 代理商: | VT6305 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

Revision 0.2

March 10, 2000

-

9-

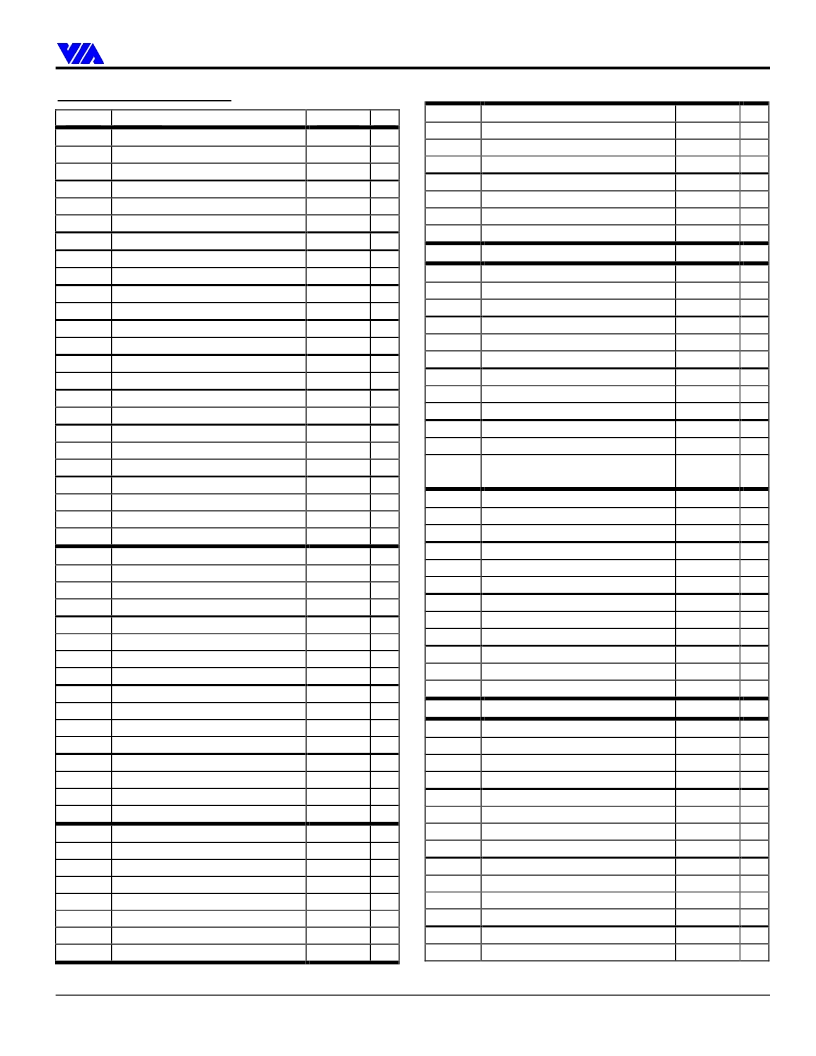

Register Overview

Technologies, Inc.

WeConnect

1394 Memory-Space Registers

Offset

0

4

8

C

10

14

18

1C

20

24

28

2C-33

34

38

3C

40

44-4F

50

54

58-5F

60-63

64

68

6C-6F

70

74

78

7C

80

84

88

8C

90

94

98

9C

A0

A4

A8

AC

B0-DB -reserved-

DC

Fairness Control

E0

Link Control Set

E4

Link Control Clear

E8

Node ID

EC

PHY Control

F0

Isochronous Cycle Timer

F4-FF

-reserved-

Heading

Version

-reserved- (GUID ROM)

Asynchronous Transmit Retries

CSR Data

CSR Compare Data

CSR Control

Configuration ROM Header

1394 Bus ID

1394 Bus Options

Global Unique ID High

Global Unique ID Low

-reserved-

Configuration ROM Map

Posted Write Address Low

Posted Write Address High

Vendor ID

-reserved-

HC Control Set

HC Control Clear

-reserved-

-reserved-

Self-ID Buffer Pointer

Self-ID Count

-reserved-

Isoch Rcv Channel Mask High Set 0000 0000 RW

Isoch Rcv Channel Mask High Clr 0000 0000 RW

Isoch Rcv Channel Mask Low Set

Isoch Rcv Channel Mask Low Clr

Interrupt Event Set

Interrupt Event Clear

Interrupt Mask Set

Interrupt Mask Clear

Isoch Xmit Interrupt Event Set

Isoch Xmit Interrupt Event Clear

Isoch Xmit Interrupt Mask Set

Isoch Xmit Interrupt Mask Clear

Isoch Rcv Interrupt Event Set

Isoch Rcv Interrupt Event Clear

Isoch Rcv Interrupt Mask Set

Isoch Rcv Interrupt Mask Clear

Default

0000 0000

RO

0000 0000 —

0000 0000 RW

0000 0000 RW

0000 0000 RW

8000 0000 RW

0000 0000 RW

3133 3934

RO

F000 0002 RW

0000 0000 RW

0000 0000 RW

00

0000 0000 RW

0000 0000

RO

0000 0000

RO

0000 0000

RO

00

0000 0000 RW

0000 0000 RW

00

00

0000 0000 RW

0000 0000

RO

00

Acc

—

—

—

—

—

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

00

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

00

—

—

100

104

108

10C

110

114

118

11C

Async Request Filter High Set

Async Request Filter High Clear

Async Request Filter Low Set

Async Request Filter Low Clear

Physical Request Filter High Set

Physical Request Filter High Clear 0000 0000 RW

Physical Request Filter Low Set

Physical Request Filter Low Clear 0000 0000 RW

120-17F -reserved-

180

Async Request Xmit Context Set

184

Async Request Xmit Context Clr

18C

Async Request Xmit Command Ptr 0000 0000 RW

1A0

Async Response Xmit Context Set 0000 0000 RW

1A4

Async Response Xmit Context Clr 0000 0000 RW

1AC

Async Response Xmit Cmd Ptr

1C0

Async Request Rcv Context Set

1C4

Async Request Rcv Context Clr

1CC

Async Request Rcv Command Ptr

1E0

Async Response Rcv Context Set

1E4

Async Response Rcv Context Clr

1EC

Async Response Rcv Command

Ptr

200

Isoch Xmit Context 0 Set

204

Isoch Xmit Context 0 Clr

20C

Isoch Xmit Context 0 Cmd Ptr

210

Isoch Xmit Context 1 Set

214

Isoch Xmit Context 1 Clr

21C

Isoch Xmit Context 1 Cmd Ptr

220

Isoch Xmit Context 1 Set

224

Isoch Xmit Context 1 Clr

22C

Isoch Xmit Context 1 Cmd Ptr

230

Isoch Xmit Context 2 Set

234

Isoch Xmit Context 2 Clr

23C

Isoch Xmit Context 2 Cmd Ptr

250-3FF -reserved-

400

Isoch Rcv Context 0 Set

404

Isoch Rcv Context 0 Clr

40C

Isoch Rcv Context 0 Command Ptr 0000 0000 RW

410

Isoch Rcv Context 0 Match

420

Isoch Rcv Context 1 Set

424

Isoch Rcv Context 1 Clr

42C

Isoch Rcv Context 1 Command Ptr 0000 0000 RW

430

Isoch Rcv Context 1 Match

440

Isoch Rcv Context 2 Set

444

Isoch Rcv Context 2 Clr

44C

Isoch Rcv Context 2 Command Ptr 0000 0000 RW

450

Isoch Rcv Context 2 Match

460

Isoch Rcv Context 3 Set

464

Isoch Rcv Context 3 Clr

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

00

—

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

00

0000 0000 RW

0000 0000 RW

—

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

0000 0000 RW

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VT6516 | 16/12 PORT 10/1000 ASE T/TX |

| VT70A144 | |

| VT74A451 | |

| VT74A901 | |

| VT77A142 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VT6508 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8 RMII PORTS OF 10/100BASE-T/TX ETHERNET SWITCH CONTROLLER |

| VT6510B | 制造商:VIA 功能描述: |

| VT6516 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:16/12 PORT 10/1000 ASE T/TX |

| VT-6-6 | 制造商:Panduit Corp 功能描述:BOLT TERM 70MM 57MM - Bulk 制造商:Panduit Corp 功能描述:Bolt Terminal 70mm 57mm |

| VT6J1 | 制造商:ROHM 制造商全稱:Rohm 功能描述:1.2V Drive Pch + Pch MOSFET |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。