- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4275 > XA3S400A-4FTG256Q (Xilinx Inc)IC FPGA SPARTAN-3A 400K 256FTBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XA3S400A-4FTG256Q |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 25/57頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3A 400K 256FTBGA |

| 產(chǎn)品培訓(xùn)模塊: | Extended Spartan 3A FPGA Family |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Spartan®-3A XA |

| LAB/CLB數(shù): | 896 |

| 邏輯元件/單元數(shù): | 8064 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 195 |

| 門(mén)數(shù): | 400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 125°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

XA Spartan-3A Automotive FPGA Family Data Sheet

DS681 (v2.0) April 22, 2011

Product Specification

31

The capacitive load (CL) is connected between the output and GND. The Output timing for all standards, as published in the

speed files and the data sheet, is always based on a CL value of zero. High-impedance probes (less than 1 pF) are used for

all measurements. Any delay that the test fixture might contribute to test measurements is subtracted from those

measurements to produce the final timing numbers as published in the speed files and data sheet.

Using IBIS Models to Simulate Load Conditions in Application

IBIS models permit the most accurate prediction of timing delays for a given application. The parameters found in the IBIS

model (VREF, RREF, and VMEAS) correspond directly with the parameters used in Table 26 (VT, RT, and VM). Do not confuse

VREF (the termination voltage) from the IBIS model with VREF (the input-switching threshold) from the table. A fourth

parameter, CREF, is always zero. The four parameters describe all relevant output test conditions. IBIS models are found in

the Xilinx development software as well as at the following link:

Delays for a given application are simulated according to its specific load conditions as follows:

1.

Simulate the desired signal standard with the output driver connected to the test setup shown in Figure 9. Use

2.

Record the time to VM.

3.

Simulate the same signal standard with the output driver connected to the PCB trace with load. Use the appropriate IBIS

model (including VREF, RREF, CREF, and VMEAS values) or capacitive value to represent the load.

4.

Record the time to VMEAS.

5.

Compare the results of steps 2 and 4. Add (or subtract) the increase (or decrease) in delay to (or from) the appropriate

Output standard adjustment (Table 25) to yield the worst-case delay of the PCB trace.

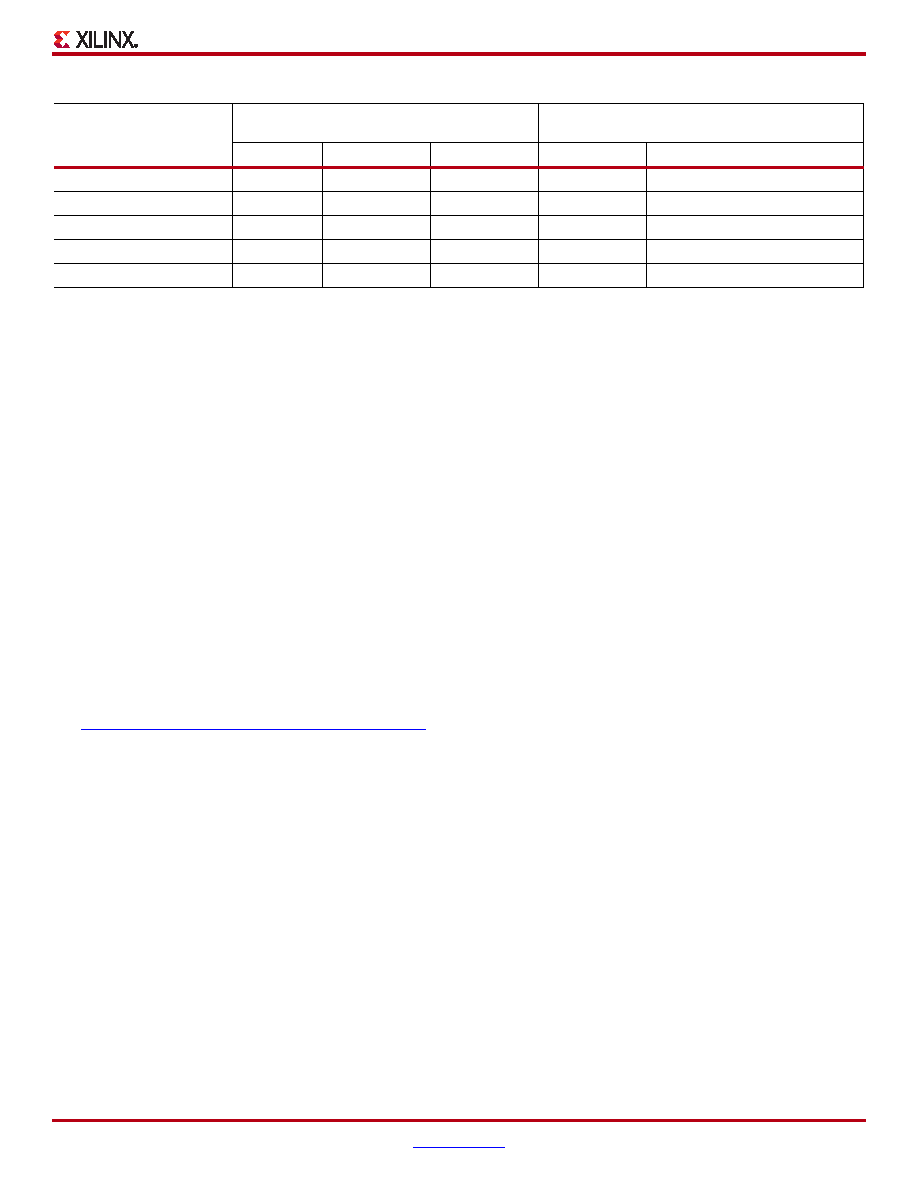

DIFF_SSTL18_II

0.9

VREF – 0.5

VREF + 0.5

50

0.9

VREF

DIFF_SSTL2_I

1.25

VREF – 0.5

VREF + 0.5

50

1.25

VREF

DIFF_SSTL2_II

1.25

VREF – 0.5

VREF + 0.5

50

1.25

VREF

DIFF_SSTL3_I

1.5

VREF – 0.5

VREF + 0.5

50

1.5

VREF

DIFF_SSTL3_II

1.5

VREF – 0.5

VREF + 0.5

50

1.5

VREF

Notes:

1.

Descriptions of the relevant symbols are as follows:

VREF – The reference voltage for setting the input switching threshold

VICM – The common mode input voltage

VM – Voltage of measurement point on signal transition

VL – Low-level test voltage at Input pin

VH – High-level test voltage at Input pin

RT – Effective termination resistance, which takes on a value of 1 M when no parallel termination is required

VT – Termination voltage

2.

The load capacitance (CL) at the Output pin is 0 pF for all signal standards.

3.

According to the PCI specification.

Table 26: Test Methods for Timing Measurement at I/Os (Cont’d)

Signal Standard

(IOSTANDARD)

Inputs

Outputs

Inputs and

Outputs

VREF (V)

VL (V)

VH (V)

RT ()VT (V)

VM (V)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RSC60DRYI-S734 | CONN EDGECARD 120PS DIP .100 SLD |

| XC6SLX25-3FT256I | IC FPGA SPARTAN 6 256FTGBGA |

| RMC60DRYI-S734 | CONN EDGECARD 120PS DIP .100 SLD |

| RSC35DTEI | CONN EDGECARD 70POS .100 EYELET |

| GCB105DHBS | CONN EDGECARD 210PS R/A .050 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA3S500E | 制造商:XILINX 制造商全稱:XILINX 功能描述:XA Spartan-3E Automotive FPGA Family Data Sheet |

| XA3S500E-4CPG132I | 功能描述:IC FPGA SPARTAN-3E 500K 132CSBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門(mén)數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4CPG132Q | 功能描述:IC FPGA SPARTAN-3E 500K 132CSBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門(mén)數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FT256Q | 功能描述:IC FPGA SPARTAN-3E 256FPBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門(mén)數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FTG256I | 功能描述:IC FPGA SPARTAN-3E 500K 256FTBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門(mén)數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。