- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4275 > XA3S400A-4FTG256Q (Xilinx Inc)IC FPGA SPARTAN-3A 400K 256FTBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XA3S400A-4FTG256Q |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 33/57頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3A 400K 256FTBGA |

| 產(chǎn)品培訓(xùn)模塊: | Extended Spartan 3A FPGA Family |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Spartan®-3A XA |

| LAB/CLB數(shù): | 896 |

| 邏輯元件/單元數(shù): | 8064 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 195 |

| 門數(shù): | 400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 125°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

XA Spartan-3A Automotive FPGA Family Data Sheet

DS681 (v2.0) April 22, 2011

Product Specification

39

Clock Buffer/Multiplexer Switching Characteristics

18 x 18 Embedded Multiplier Timing

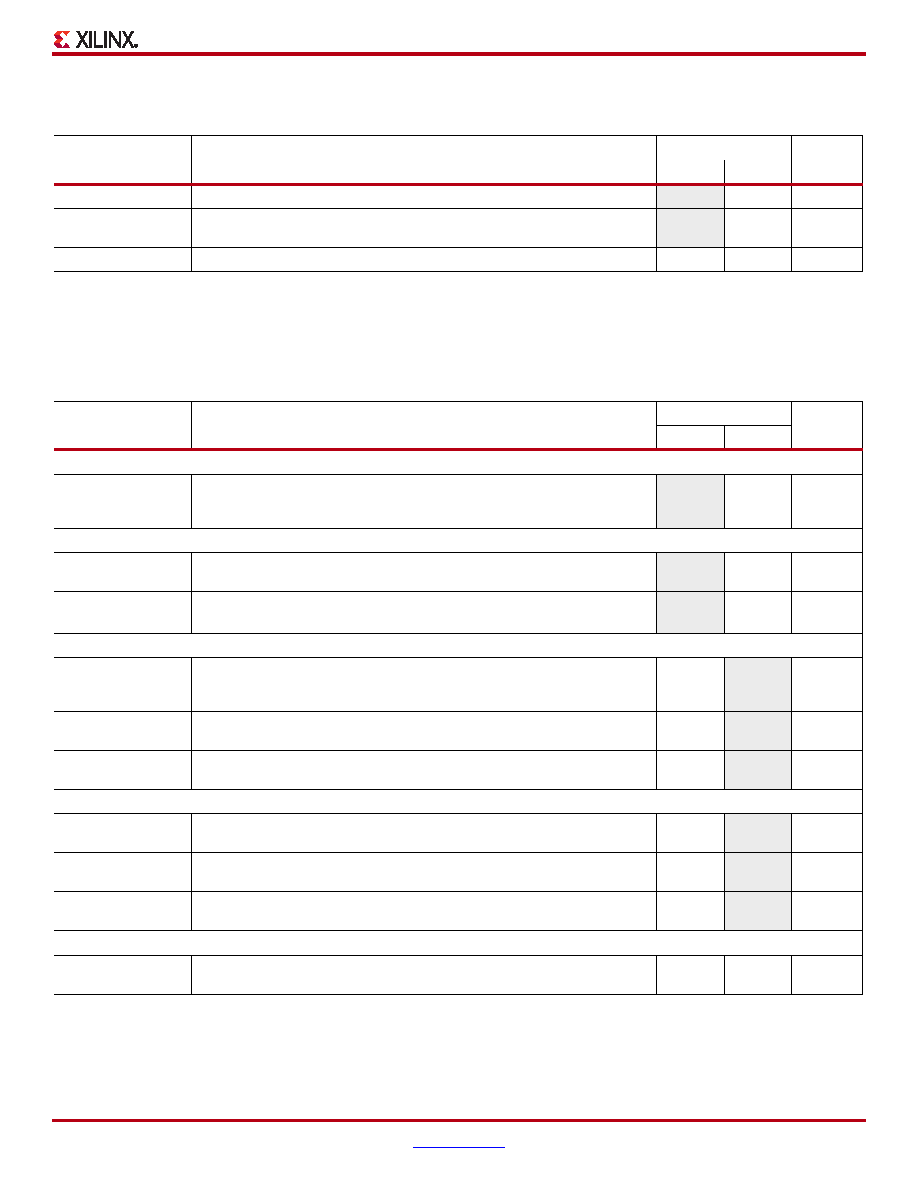

Table 32: Clock Distribution Switching Characteristics

Symbol

Description

Speed Grade: -4

Units

Min

Max

TGIO

Global clock buffer (BUFG, BUFGMUX, BUFGCE) I input to O-output delay

–0.23

ns

TGSI

Global clock multiplexer (BUFGMUX) select S-input setup to I0 and I1 inputs.

Same as BUFGCE enable CE-input

–0.63

ns

FBUFG

Frequency of signals distributed on global buffers (all sides)

0

333

MHz

Notes:

1.

The numbers in this table are based on the operating conditions set forth in Table 8.

Table 33: 18 x 18 Embedded Multiplier Timing

Symbol

Description

Speed Grade: -4

Units

Min

Max

Combinatorial Delay

TMULT

Combinational multiplier propagation delay from the A and B inputs to the P

outputs, assuming 18-bit inputs and a 36-bit product (AREG, BREG, and

PREG registers unused)

–4.88

ns

Clock-to-Output Times

TMSCKP_P

Clock-to-output delay from the active transition of the CLK input to valid data

appearing on the P outputs when using the PREG register(2,3)

–1.30

ns

TMSCKP_A

TMSCKP_B

Clock-to-output delay from the active transition of the CLK input to valid data

appearing on the P outputs when using either the AREG or BREG register(2,4)

–4.97

ns

Setup Times

TMSDCK_P

Data setup time at the A or B input before the active transition at the CLK

when using only the PREG output register (AREG, BREG registers

unused)(3)

3.98

–ns

TMSDCK_A

Data setup time at the A input before the active transition at the CLK when

using the AREG input register(4)

0.00

–ns

TMSDCK_B

Data setup time at the B input before the active transition at the CLK when

using the BREG input register(4)

0.00

–ns

Hold Times

TMSCKD_P

Data hold time at the A or B input after the active transition at the CLK when

using only the PREG output register (AREG, BREG registers unused)(3)

0.00

–ns

TMSCKD_A

Data hold time at the A input after the active transition at the CLK when using

the AREG input register(4)

0.45

–ns

TMSCKD_B

Data hold time at the B input after the active transition at the CLK when using

the BREG input register(4)

0.45

–ns

Clock Frequency

FMULT

Internal operating frequency for a two-stage 18x18 multiplier using the AREG

and BREG input registers and the PREG output register(1)

0

250

MHz

Notes:

1.

Combinational delay is less and pipelined performance is higher when multiplying input data with less than 18 bits.

2.

The PREG register is typically used in both single-stage and two-stage pipelined multiplier implementations.

3.

The PREG register is typically used when inferring a single-stage multiplier.

4.

Input registers AREG or BREG are typically used when inferring a two-stage multiplier.

5.

The numbers in this table are based on the operating conditions set forth in Table 8.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RSC60DRYI-S734 | CONN EDGECARD 120PS DIP .100 SLD |

| XC6SLX25-3FT256I | IC FPGA SPARTAN 6 256FTGBGA |

| RMC60DRYI-S734 | CONN EDGECARD 120PS DIP .100 SLD |

| RSC35DTEI | CONN EDGECARD 70POS .100 EYELET |

| GCB105DHBS | CONN EDGECARD 210PS R/A .050 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XA3S500E | 制造商:XILINX 制造商全稱:XILINX 功能描述:XA Spartan-3E Automotive FPGA Family Data Sheet |

| XA3S500E-4CPG132I | 功能描述:IC FPGA SPARTAN-3E 500K 132CSBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4CPG132Q | 功能描述:IC FPGA SPARTAN-3E 500K 132CSBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FT256Q | 功能描述:IC FPGA SPARTAN-3E 256FPBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XA3S500E-4FTG256I | 功能描述:IC FPGA SPARTAN-3E 500K 256FTBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-3E XA 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。