- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75R06DIB (EXAR CORP) SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER PDF資料下載

參數(shù)資料

| 型號: | XRT75R06DIB |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PBGA217 |

| 封裝: | 23 X 23 MM, BGA-217 |

| 文件頁數(shù): | 83/105頁 |

| 文件大?。?/td> | 591K |

| 代理商: | XRT75R06DIB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁當(dāng)前第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁

á

SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

XRT75R06D

REV. 1.0.0

78

viewed as a 12-Channel DS3/STS-1 to STS-12 Mapper IC. Continuing on with this line of thought, if a Mapper

IC is configured to receive an STS-N signal, and (from this STS-N signal) de-map and output N DS3 signals

(towards the DS3 facility), then it will typically do so in the following manner.

In many cases, the Mapper IC will output this DS3 signal, using both a "Data-Signal" and a "Clock-Signal".

In many cases, the Mapper IC will output the contents of an entire STS-1 data-stream via the Data-Signal.

However, as the Mapper IC output this STS-1 data-stream, it will typically supply clock pulses (via the Clock-

Signal output) coincident to whenever a DS3 bit is being output via the Data-Signal. In this case, the Mapper

IC will NOT supply a clock pulse coincident to when a TOH, POH, or any "non-DS3 data-bit" is being output

via the "Data-Signal".

Now, since the Mapper IC will output the entire STS-1 data stream (via the Data-Signal), the output Clock-

Signal will be of the form such that it has a period of 19.3ns (e.g., a 51.84MHz clock signal). However, the

Mapper IC will still generate approximately 44,736,000 clock pulses during any given one second period.

Hence, the clock signal that is output from the Mapper IC will be a horribly gapped 44.736MHz clock signal.

One can view such a clock signal as being a very-jittery 44.736MHz clock signal. This jitter that exists within

the "Clock-Signal" is referred to as "Clock-Gapping" Jitter. A more detailed discussion on how the user must

handle this type of jitter is presented in “Section 8.8.2, Recommendations on Pre-Processing the Gapped

Clocks (from the Mapper/ASIC Device) prior to routing this DS3 Clock and Data-Signals to the Transmit Inputs

of the LIU” on page 89.

8.5

A Review of the Category I Intrinsic Jitter Requirements (per Telcordia GR-253-CORE) for DS3

applications

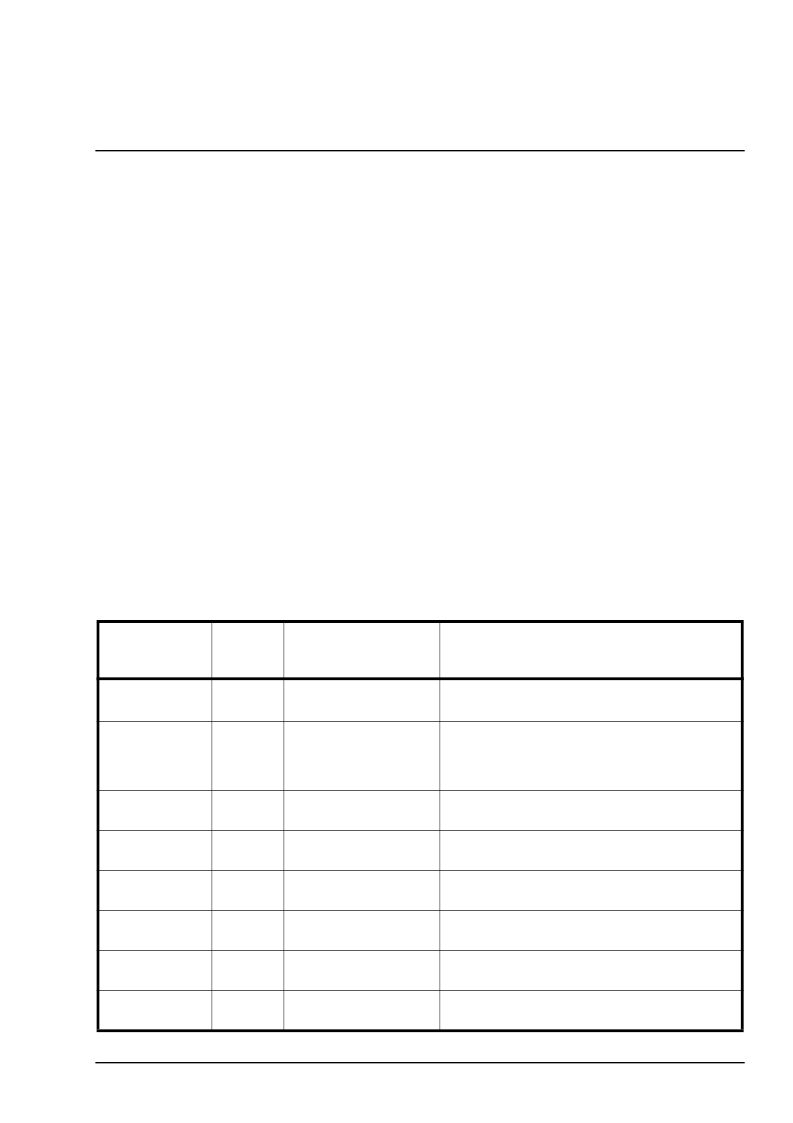

The "Category I Intrinsic Jitter Requirements" per Telcordia GR-253-CORE (for DS3 applications) mandates

that the user perform a large series of tests against certain specified "Scenarios". These "Scenarios" and their

corresponding requirements is summarized in Table 19, below.

T

ABLE

19: S

UMMARY

OF

"C

ATEGORY

I I

NTRINSIC

J

ITTER

R

EQUIREMENT

PER

T

ELCORDIA

GR-253-CORE,

FOR

DS3

APPLICATIONS

S

CENARIO

D

ESCRIPTION

S

CENARIO

N

UMBER

T

ELCORDIA

GR-253-CORE

C

ATEGORY

I I

NTRINSIC

J

ITTER

R

EQUIREMENTS

C

OMMENTS

DS3 De-Mapping

Jitter

0.4UI-pp

Includes effects of De-Mapping and Clock Gapping Jit-

ter

Single Pointer

Adjustment

A1

0.3UI-pp + Ao

Includes effects of Jitter from Clock-Gapping, De-Map-

ping and Pointer Adjustments.NOTE: Ao is the amount

of intrinsic jitter that was measured during the "DS3 De-

Mapping Jitter" phase of the Test.

Pointer Bursts

A2

1.3UI-pp

Includes effects of Jitter from Clock-Gapping, De-Map-

ping and Pointer Adjustments.

Phase Transients

A3

1.2UI-pp

Includes effects of Jitter from Clock-Gapping, De-Map-

ping and Pointer Adjustments.

87-3 Pattern

A4

1.0UI-pp

Includes effects of Jitter from Clock-Gapping, De-Map-

ping and Pointer Adjustments.

87-3 Add

A5

1.3UI-pp

Includes effects of Jitter from Clock-Gapping, De-Map-

ping and Pointer Adjustments.

87-3 Cancel

A5

1.3UI-pp

Includes effects of Jitter from Clock-Gapping, De-Map-

ping and Pointer Adjustments.

Continuous Pattern

A4

1.0UI-pp

Includes effects of Jitter from Clock-Gapping, De-Map-

ping and Pointer Adjustments.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75R06 | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75R06IB | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75R12D | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75R12DIB | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75R12 | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75R06DIB-F | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 6 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT75R06ES | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 6CH T3/E3/STS1LIU+JA 3.3V W/REDUNDANCY RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75R06IB | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 6CH E3/DS3/STS1 LIU+Jitter Attenuato RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75R06IB208 | 制造商:Exar Corporation 功能描述:Line Interface Unit 51.84Mbps DS3/E3/STS-1 Parallel 217-Pin BGA |

| XRT75R06IB-F | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 6 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。