- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄2121 > XRT83VL38IB-F (Exar Corporation)IC LIU SH T1/E1/J1 OCTAL 225BGA PDF資料下載

參數(shù)資料

| 型號: | XRT83VL38IB-F |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 90/95頁 |

| 文件大小: | 0K |

| 描述: | IC LIU SH T1/E1/J1 OCTAL 225BGA |

| 標(biāo)準(zhǔn)包裝: | 84 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動器/接收器數(shù): | 8/8 |

| 規(guī)程: | E1 |

| 電源電壓: | 3.14 V ~ 3.47 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 225-BGA |

| 供應(yīng)商設(shè)備封裝: | 225-BGA(19x19) |

| 包裝: | 托盤 |

| 其它名稱: | 1016-1481 XRT83VL38IB-F-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁當(dāng)前第90頁第91頁第92頁第93頁第94頁第95頁

XRT83VL38

86

OCTAL T1/E1/J1 LH/SH TRANSCEIVER WITH CLOCK RECOVERY AND JITTER ATTENUATOR

REV. 1.0.1

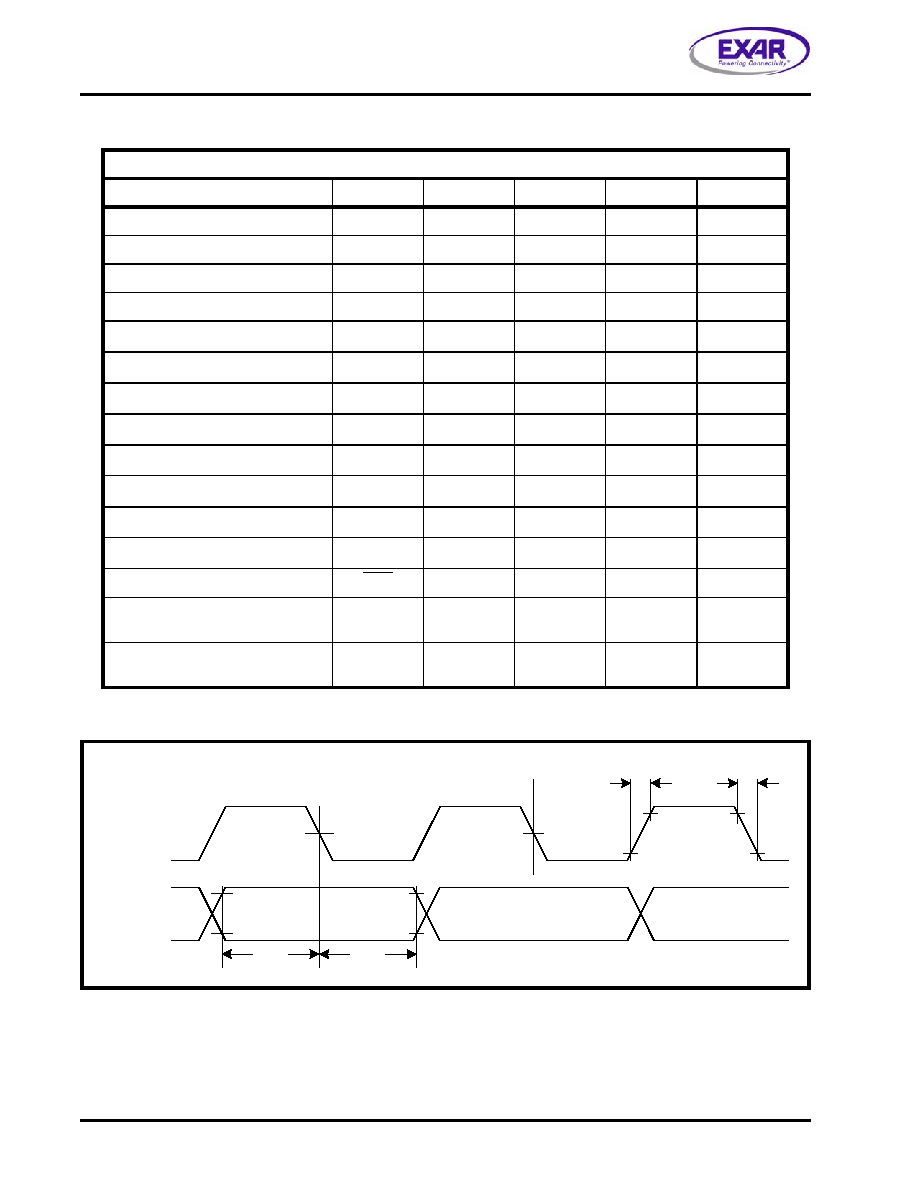

TABLE 55: AC ELECTRICAL CHARACTERISTICS

VDD=3.3V±5%, TA=25°C, UNLESS OTHERWISE SPECIFIED

PARAMETER

SYMBOL

MIN.

TYP.

MAX.

UNITS

E1 MCLK Clock Frequency

-

2.048

MHz

T1 MCLK Clock Frequency

-

1.544

MHz

MCLK Clock Duty Cycle

40

-

60

%

MCLK Clock Tolerance

-

±50

-

ppm

TCLK Duty Cycle

TCDU

30

50

70

%

Transmit Data Setup Time

TSU

50

-

ns

Transmit Data Hold Time

THO

30

-

ns

TCLK Rise Time(10%/90%)

TCLKR

-

40

ns

TCLK Fall Time(90%/10%)

TCLKF

-

40

ns

RCLK Duty Cycle

RCDU

45

50

55

%

Receive Data Setup Time

RSU

150

-

ns

Receive Data Hold Time

RHO

150

-

ns

RCLK to Data Delay

RDY

-

40

ns

RCLK Rise Time(10% to 90%) with

25pF Loading.

RCLKR

-

40

ns

RCLK Fall Time(90% to 10%) with

25pF Loading.

RCLKF

40

ns

FIGURE 35. TRANSMIT CLOCK AND INPUT DATA TIMING

TCLK

R

TCLK

F

TCLK

TPOS/TDATA

or

TNEG

T

SU

T

HO

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT83VSH28IB | IC LIU SH E1 OCTAL 225BGA |

| XRT83VSH314IB-F | IC LIU SH T1/E1/J1 14CH 304TBGA |

| XRT83VSH316IB | IC LIU SH T1/E1/J1 16CH 316STBGA |

| XRT83VSH38IB | IC LIU SH T1/E1/J1 8CH 225BGA |

| XRT85L61IG | IC BITS CLOCK EXTRACTOR 28TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT83VSH28 | 制造商:EXAR 制造商全稱:EXAR 功能描述:8-CHANNEL E1 SHORT-HAUL LINE INTERFACE UNIT |

| XRT83VSH28ES | 功能描述:外圍驅(qū)動器與原件 - PCI 8 CH E1 LIU SH (low cost version) RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT83VSH28IB | 功能描述:接口 - 專用 8 Ch T1/E1 Framer RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

| XRT83VSH28IB-F | 功能描述:外圍驅(qū)動器與原件 - PCI 8 Channel 1.8V-3.3V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT83VSH28IB-F | 制造商:Exar Corporation 功能描述:T1/E1 LIU IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。