- 您現(xiàn)在的位置:買賣IC網 > PDF目錄376464 > XRT91L81 (Exar Corporation) 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號: | XRT91L81 |

| 廠商: | Exar Corporation |

| 英文描述: | 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| 中文描述: | 2.488/2.666GBPS OC-48/STM-16的SONET / SDH收發(fā)器 |

| 文件頁數(shù): | 8/40頁 |

| 文件大小: | 264K |

| 代理商: | XRT91L81 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

XRT91L81

2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER

REV. P1.0.3

PRELIMINARY

6

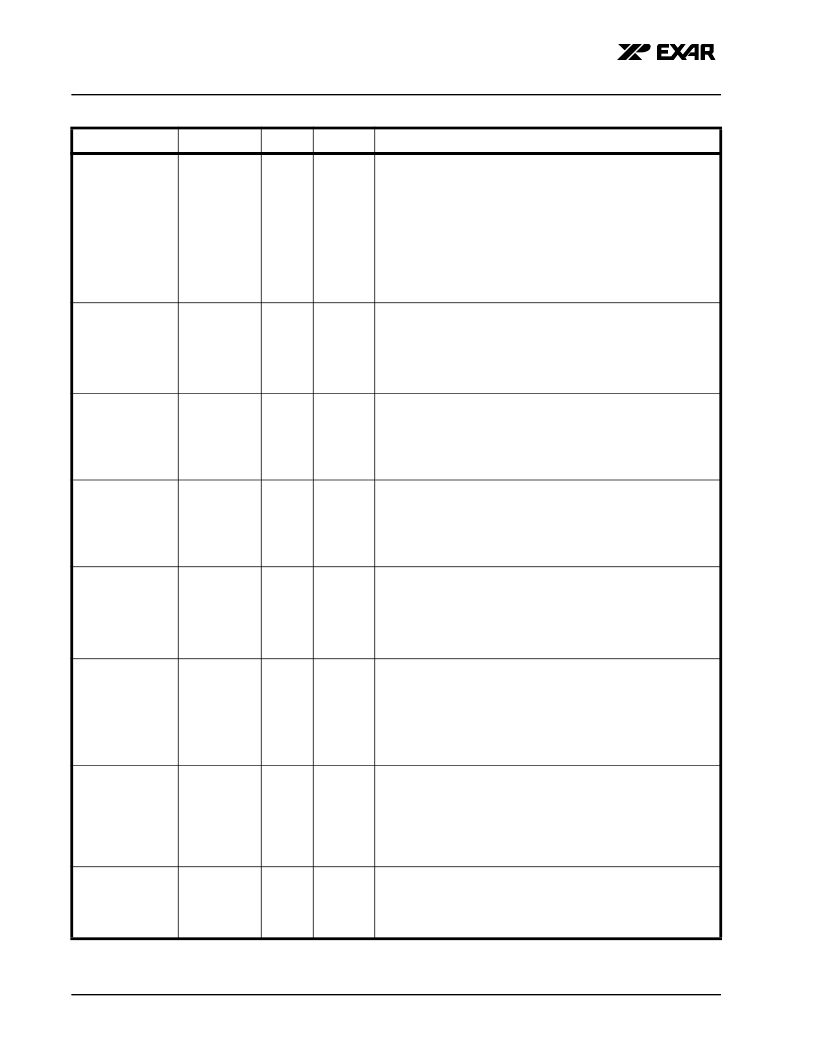

TRANSMITTER SECTION

N

AME

L

EVEL

T

YPE

P

IN

D

ESCRIPTION

TXDI0P

TXDI0N

TXDI1P

TXDI1N

TXDI2P

TXDI2N

TXDI3P

TXDI3N

LVDS

I

H13

J13

K14

L14

K13

L13

M14

N14

Transmit Parallel Data Input

The 622Mbps 4-bit parallel transmit input data should be

applied to the transmitters simultaneously referenced to the ris-

ing edge of the TXCLKI input. The 4-bit parallel interface is

multiplexed into the transmit serial output interface MSB first

(TXDI3P/N).

N

OTE

:

The XRT91L81 can accept 666Mbps 4-bit parallel

transmit input data for Forward Error Correction (FEC)

Applications.

TXCLKIP

TXCLKIN

LVDS

I

H14

J14

Transmit Input Clock

622MHz input clock reference for the 4-bit parallel transmit

input data TXDIP/N[3:0].

N

OTE

:

The XRT91L81 can accept a 666MHz transmit input

clock for Forward Error Correction (FEC) Applications.

TXOP

TXON

CMLDIFF

O

L2

K2

Transmit Serial Data Output

The transmit serial data stream is generated by multiplexing the

4-bit parallel transmit input data into a 2.488Gbps serial data

stream. In Forward Error Correction, the transmit serial data

stream is 2.666Gbps.

TXO2P

TXO2N

CMLDIFF

O

K1

L1

Secondary Transmit Serial Data Output Port

The secondary transmit serial data port can output the TXO

serial data stream or it can output the transmit output clock.

See the pin description of TXO2_SEL and TXO2DIS for more

details.

TXO2_SEL

LVTTL

I

N3

Secondary Transmit Select

Hardware Mode

The TXO2_SEL pin is used to determine the

output contents of the secondary transmit serial data output.

"Low" = 2.488Gbit/s Serial Output Data

"High" = Transmit Output Clock (2.488/2.666 GHz)

TXO2DIS

LVTTL

I

N1

Secondary Transmit Disable

Hardware Mode

The TXO2DIS pin is used to disable the sec-

ondary transmit serial data output pins. If the secondary trans-

mit serial data is disabled, both TXO2P/N are pulled "High".

"Low" = TXO2 is enabled

"High" = Diabled

REFCLKP

REFCLKN

LVPECL

I

P6

N6

Reference Clock Input

This differential input clock reference is used for the transmit

clock multiplier unit (CMU) to provide the necessary high speed

clock reference for this device. Pin REFFREQSEL determines

the value used as the reference. See Pin REFFREQSEL for

more details.

VCXO_INP

VCXO_INN

LVPECL

I

P4

N4

Voltage Controled Oscillator Input

This differential input clock is used for the transmit PLL jitter

attenuation. Pin REFFREQSEL determines the value used as

the reference. See Pin REFFREQSEL for more details.

相關PDF資料 |

PDF描述 |

|---|---|

| XRT91L81IB | 2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82 | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82IB | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT94L31_07 | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC |

| XRT94L31 | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L81IB | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666GBPS OC-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT91L82ES | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L82IB | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L82IB-F | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。