- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄156551 > 37C669 (SMSC Corporation) DIODE SCHOTTKY SINGLE 25V 200mW 0.5V-vf 200mA-IFM 30mA-IF 2uA-IR SOD-323 3K/REEL PDF資料下載

參數(shù)資料

| 型號(hào): | 37C669 |

| 廠商: | SMSC Corporation |

| 英文描述: | DIODE SCHOTTKY SINGLE 25V 200mW 0.5V-vf 200mA-IFM 30mA-IF 2uA-IR SOD-323 3K/REEL |

| 中文描述: | 電腦98/99順從超級(jí)I / O軟盤(pán)控制器與紅外線支持 |

| 文件頁(yè)數(shù): | 81/164頁(yè) |

| 文件大小: | 621K |

| 代理商: | 37C669 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)當(dāng)前第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)

23

DIGITAL OUTPUT REGISTER (DOR)

Address 3F2 READ/WRITE

The DOR controls the drive select and motor

enables of the disk interface outputs. It also

contains the enable for the DMA logic and

contains a software reset bit. The contents of

the DOR are unaffected by a software reset.

The DOR can be written to at any time.

BIT 0 and 1 DRIVE SELECT

These two bit a are binary encoded for the four

drive selects DS0-DS3, thereby allowing only

one drive to be selected at one time.

BIT 2 nRESET

A logic "0" written to this bit resets the Floppy

disk controller.

This reset will remain active

until a logic "1" is written to this bit.

This

software reset does not affect the DSR and CCR

registers, nor does it affect the other bits of the

DOR register.

The minimum reset duration

required is 100ns, therefore toggling this bit by

consecutive writes to this register is a valid

method of issuing a software reset.

BIT 3 DMAEN

PC/AT and Model 30 Mode:

Writing this bit to logic "1" will enable the DRQ,

nDACK, TC and FINTR outputs. This bit being

a logic "0" will disable the nDACK and TC

inputs, and hold the DRQ and FINTR outputs in

a high impedance state. This bit is a logic "0"

after a reset and in these modes.

PS/2 Mode: In this mode the DRQ, nDACK, TC

and FINTR pins are always enabled. During a

reset, the DRQ, nDACK, TC, and FINTR pins

will remain enabled, but this bit will be cleared to

a logic "0".

BIT 4 MOTOR ENABLE 0

This bit controls the MTR0 disk interface output.

A logic "1" in this bit will cause the output pin to

go active.

BIT 5 MOTOR ENABLE 1

This bit controls the MTR1 disk interface output.

A logic "1" in this bit will cause the output pin to

go active.

BIT 6 MOTOR ENABLE 2

This bit controls the MTR2 disk interface output.

A logic "1" in this bit will cause the output pin to

go active.

BIT 7 MOTOR ENABLE 3

This bit controls the MTR3 disk interface output.

A logic "1" in this bit causes the output to go

active.

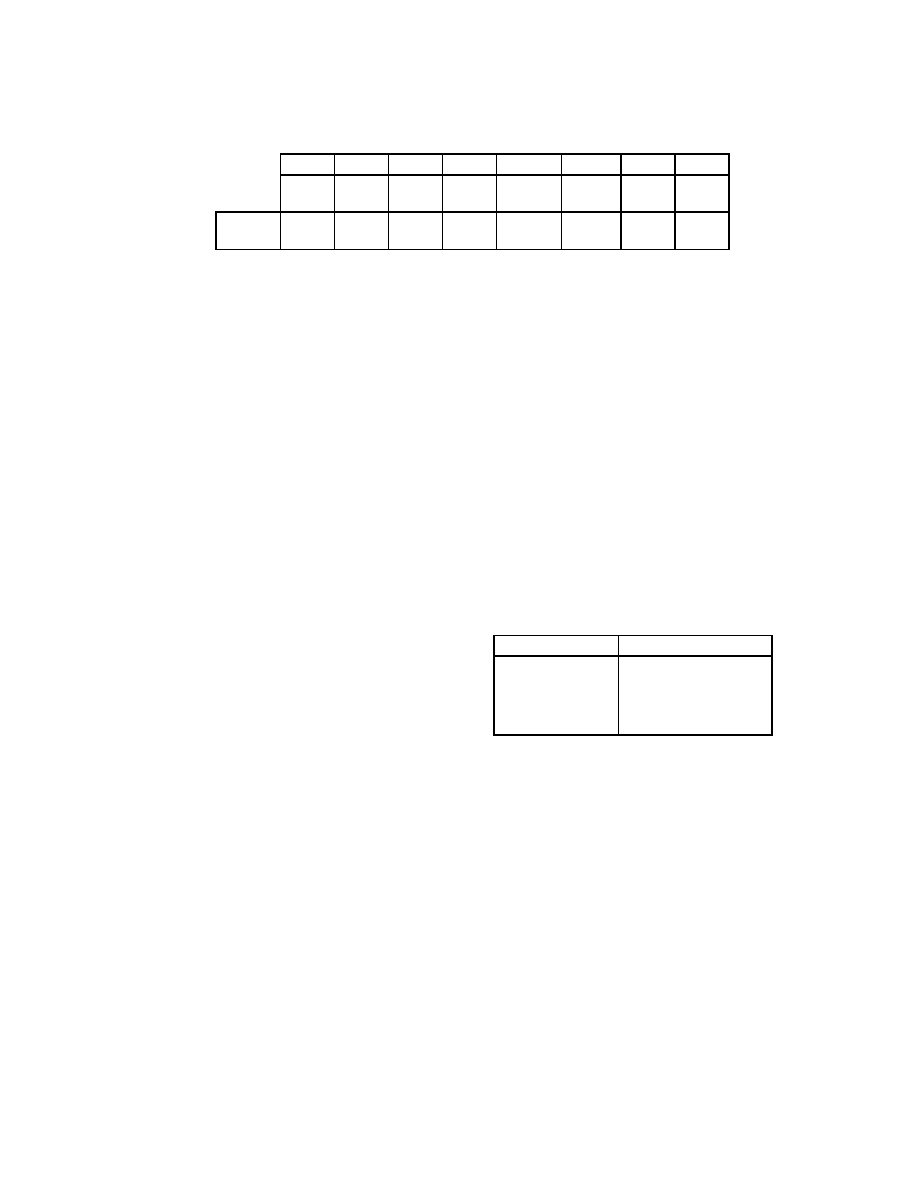

Table 3 - Drive Activation Values

7

6

5

4

3

2

1

0

MOT

EN3

MOT

EN2

MOT

EN1

MOT

EN0

DMAEN nRESET DRIVE

SEL1

DRIVE

SEL0

RESET

COND.

0

DRIVE

DOR VALUE

0

1

2

3

1CH

2DH

4EH

8FH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 37C672 | ENHANCED SUPER I/O CONTROLLER WITH FAST IR |

| 37C67X | ENHANCED SUPER I/O CONTROLLER WITH FAST IR |

| 37C957FR | ULTRA I/O CONTROLLER FOR PORTABLE APPLICATIONS |

| 37FMA1-ABW31N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

| 37FML1-BEW31N | SPECIAL SWITCH-PIEZO SWITCH, SPST, MOMENTARY, 0.2A, 24VDC, PANEL MOUNT-THREADED |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 37C672 | 制造商:SMSC 制造商全稱:SMSC 功能描述:ENHANCED SUPER I/O CONTROLLER WITH FAST IR |

| 37C67X | 制造商:SMSC 制造商全稱:SMSC 功能描述:ENHANCED SUPER I/O CONTROLLER WITH FAST IR |

| 37C-6BH-5-5 | 制造商:Birtcher Products 功能描述: |

| 37C72U-185 | 制造商:White-Rodgers 功能描述: |

| 37C73U-170 | 制造商:White-Rodgers 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。