- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6636BC (Analog Devices, Inc.) 150 MSPS Wideband Digital Down-Converter (DDC) PDF資料下載

參數(shù)資料

| 型號: | AD6636BC |

| 廠商: | Analog Devices, Inc. |

| 元件分類: | 數(shù)字上/下變頻 |

| 英文描述: | 150 MSPS Wideband Digital Down-Converter (DDC) |

| 中文描述: | 150MSPS的寬帶數(shù)字下變頻器(DDC) |

| 文件頁數(shù): | 66/72頁 |

| 文件大小: | 1629K |

| 代理商: | AD6636BC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁當(dāng)前第66頁第67頁第68頁第69頁第70頁第71頁第72頁

AD6636

<7:5>: AGC Word Length Control Bits. These bits define the

word length of the AGC output. The output word can be 4 to 8,

10, 12, or 16 bits wide. Table 41 shows the possible selections.

Rev. 0 | Page 66 of 72

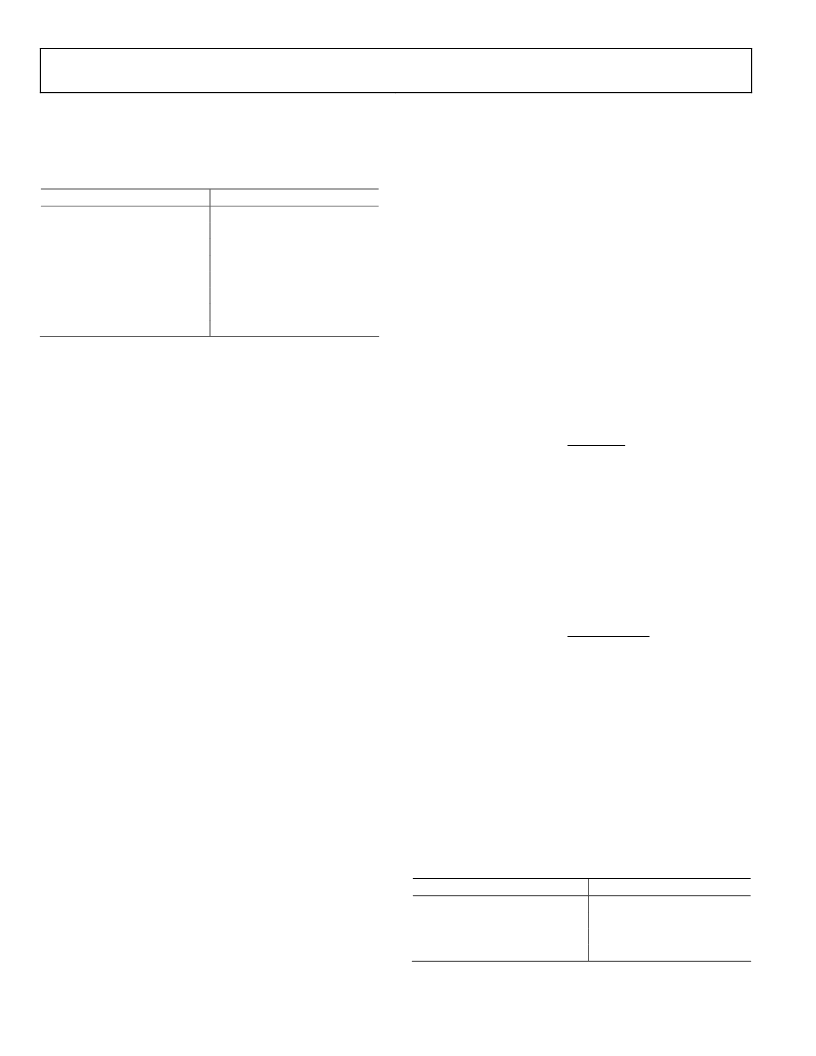

Table 41. AGC Word Length Control Bits

AGC Control Bits <7:5>

000

001

010

011

100

101

110

111

Output Word Length (Bits)

16

12

10

8

7

6

5

4

<4>: AGC Mode Bit. When this bit is set, the AGC operates to

maintain a desired signal level. When this bit is cleared, it

operates to maintain a constant clipping level. See the

Automatic Gain Control section for details about these modes.

<3>: AGC Sync Now Bit. This bit is used to synchronize a

particular AGC irrespective of the channel through the

programming ports (microport or serial port). When this bit is

set, the AGC block updates a new output sample (RSSI sample)

and starts working toward a new update sample.

<2>: Initialize on Sync Bit. This bit is used to determine whether

or not the AGC should initialize on a sync. When this bit is set,

during a synchronization the CIC filter is cleared and new

values for CIC decimation, number of averaging samples, CIC

scale, signal gain Gs’ gain K, and pole parameter P are loaded.

When Bit <2> = 0, the above-mentioned parameters are not

updated, and the CIC filter is not cleared. In both cases an AGC

update sample is output from the CIC filter and the decimator

starts operating towards the next output sample whenever a

sync occurs.

<1>: First Sync Only. This bit is used to ignore repetitive

synchronization signals. In some applications, the synchroniza-

tion signal occurs periodically. If this bit is cleared, each

synchronization request resynchronizes the AGC. If this bit is

set, only the first occurrence causes the AGC to synchronize

and updates the AGC gain values periodically, depending on the

decimation factor of the AGC CIC filter.

<0>: AGC Bypass Bit. When this bit is set, the AGC section is

bypassed. The N-bit representation from the interpolating half-

band filters is still reduced to a lower bit width representation as

set by Bits <7:5> of the AGC control register. A truncation at the

output of the AGC accomplishes this task.

AGC Hold-Off Register <15:0>

The AGC hold-off counter is loaded with the value written to

this address when either a soft sync or pin sync comes into the

channel. The counter begins counting down. When it reaches 1,

a sync is sent to the AGC. This sync might or might not

initialize the AGC, as defined by the control word. The AGC

loop is updated with a new sample from the CIC filter whenever

a sync occurs. If this register is Logic 1, the AGC is updated

immediately when the sync occurs. If this register Logic 0, the

AGC cannot be synchronized.

AGC Update Decimation <11:0>

This 12-bit register sets the AGC decimation ratio from 1 to

4096. An appropriate scaling factor should be set to avoid loss of

bits. The decimation ratio is given by the decimal value of the

AGC update decimation<11:0> register contents plus 1, that is,

12’0x000 describes a decimation ratio of 1, and 12’0xFFF

describes a decimation ratio of 4096.

AGC Signal Gain <11:0>

This register is used to set the initial value for a signal gain used

in the gain multiplier. This 12-bit value sets the initial signal

gain in the range of 0 dB and 96.296 dB in steps of 0.024 dB.

Initial signal gain (SG) in dB should be converted to a register

setting using the following formula:

Register Value

=

round

×

256

)

log

20

10

SG

AGC Error Threshold <11:0>

This 12-bit register is the comparison value used to determine

which loop gain value (K

1

or K

2

) to use for optimum operation.

When the magnitude-of-error signal is less than the AGC error

threshold value, then K

1

is used; otherwise, K

2

is used. The word

format of the AGC error threshold register is four bits to the left

of the binary point and eight bits to the right. See the Automatic

Gain Control section for details.

Register Value

=

round

×

256

)

log

20

10

Threshold

Error

AGC Average Samples <5:0>

This 6-bit register contains the scale used for the CIC filter and

the number of power samples to be averaged before being sent

to the CIC filter.

<5:2>: CIC Scale. This 4-bit word defines the scale used for the

CIC filter. Each increment of this word increases the CIC scale

by 6.02 dB.

<1:0>: Number of AGC Average Samples. This defines the

number of samples to be averaged before they are sent to the

CIC decimating filter. See Table 42.

Table 42. Number of AGC Average Samples

AGC Average Samples <1:0>

00

01

10

11

Number of Samples Taken

1

2

3

4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD6636CBCZ1 | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD6636PCB | 150 MSPS Wideband Digital Down-Converter (DDC) |

| AD664(中文) | Monolithic 12-Bit Quad DAC(單片12位四D/A轉(zhuǎn)換器) |

| AD6640 | 12-Bit, 65 MSPS IF Sampling A/D Converter |

| AD6640AST | 12-Bit, 65 MSPS IF Sampling A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6636BC/PCB | 制造商:Analog Devices 功能描述:Evaluation Board For 150MSPS Wideband Digital Down-Converter 制造商:Analog Devices 功能描述:EVALUATION BOARD AD6636 - Bulk |

| AD6636BC/PCBZ | 制造商:Analog Devices 功能描述:Evaluation Kit For 150 MSPS, Wide Band, Digital Down Converter 制造商:Analog Devices 功能描述:EVALUATION BOARD AD6636 - Bulk |

| AD6636CBC | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD6636CBCZ | 功能描述:IC DIGITAL DWNCONV 4CH 256CSPBGA RoHS:是 類別:RF/IF 和 RFID >> RF 混頻器 系列:AD6636 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:100 系列:- RF 型:W-CDMA 頻率:2.11GHz ~ 2.17GHz 混頻器數(shù)目:1 增益:17dB 噪音數(shù)據(jù):2.2dB 次要屬性:- 電流 - 電源:11.7mA 電源電壓:2.7 V ~ 3.3 V 包裝:托盤 封裝/外殼:12-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:12-QFN-EP(3x3) |

| AD6636CBCZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:150 MSPS Wideband Digital Down-Converter (DDC) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。