- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376965 > DS21Q50N Telecommunication IC PDF資料下載

參數(shù)資料

| 型號(hào): | DS21Q50N |

| 英文描述: | Telecommunication IC |

| 中文描述: | 通信集成電路 |

| 文件頁(yè)數(shù): | 21/99頁(yè) |

| 文件大小: | 325K |

| 代理商: | DS21Q50N |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)

DS21Q50

Page 21 of 99

6. HOST INTERFACE PORT

The DS21Q50 is controlled via either a non–multiplexed bus, a multiplexed bus or serial interface bus by an

external microcontroller or microprocessor. The device can operate with either Intel or Motorola bus timing

configurations. See Table 6-1 for a description of the bus configurations. All Motorola bus signals are listed in

parenthesis (). See the timing diagrams in the A.C. Electrical Characteristics in Section 22 for more details.

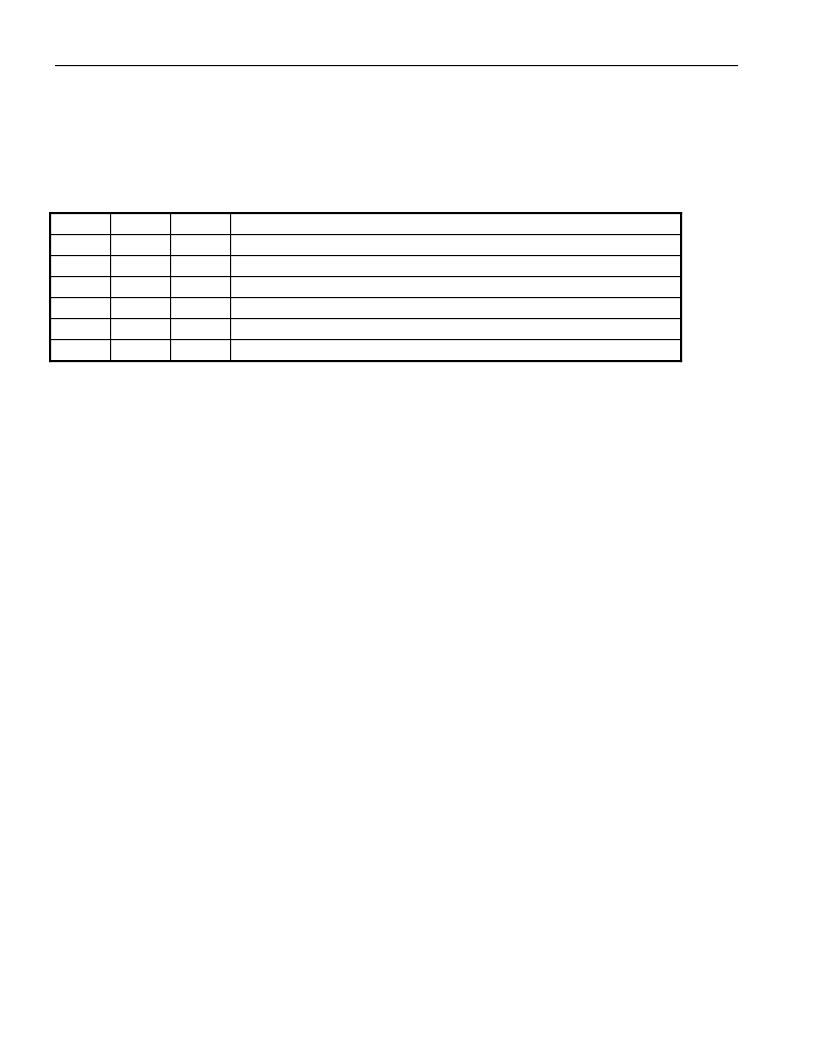

Table 6-1 BUS MODE SELECT

PBTS

BTS1

BTS0

0

0

0

0

0

1

1

0

0

1

0

1

Motorola Non-Multiplexed

X

1

0

X

1

1

TEST (Outputs High Z)

6.1 PARALLEL PORT OPERATION

When using the parallel interface on the DS21Q50 (BTS1 = 0) the user has the option for either multiplexed bus

operation (BTS1 = 0, BTS0 = 0) or non-multiplexed bus operation (BTS1 = 0, BTS0 = 1). The DS21Q50 can

operate with either Intel or Motorola bus timing configurations. If the PBTS pin is tied low, Intel timing will be

selected; if tied high, Motorola timing will be selected. All Motorola bus signals are listed in parenthesis (). See

the timing diagrams in section 24 for more details.

6.2 SERIAL PORT OPERATION

Setting BTS1 pin = 1 and the BTS0 pin = 0 enables the serial bus interface on the DS21Q50. Port read/write

timing is unrelated to the system transmit and receive timing, allowing asynchronous reads or writes by the host.

See Section 24 for the AC timing of the serial port. All serial port accesses are LSB first. See Figure 6-1,

Figure 6-2, Figure 6-3, and Figure 6-4 for more details.

Reading or writing to the internal registers requires writing one address/command byte prior to transferring

register data. The first bit written (LSB) of the address/command byte specifies whether the access is a read (1)

or a write (0). The next 5 bits identify the register address. The next bit is reserved and must be set to 0 for

proper operation. The last bit (MSB) of the address/command byte enables the burst mode when set to 1. The

burst mode causes all registers to be consecutively written or read.

All data transfers are initiated by driving the CS* input low. When Input Clock-Edge Select (ICES) is low, input

data is latched on the rising edge of SCLK and when ICES is high, input data is latched on the falling edge of

SCLK. When Output Clock-Edge Select (OCES) is low, data is output on the falling edge of SCLK and when

OCES is high, data is output on the rising edge of SCLK. Data is held until the next falling or rising edge. All

data transfers are terminated if the CS* input transitions high. Port control logic is disabled and SDO is tri-stated

when CS* is high.

Figure 6-1 SERIAL PORT OPERATION MODE 1

ICES = 1 (sample SDI on the falling edge of SCLK)

OCES = 1 (update SDO on rising edge of SCLK)

Parallel Port Mode

Intel Multiplexed

Intel Non-Multiplexed

Motorola Multiplexed

Serial

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS21Q55DK | Quad T1/E1/J1 Transceiver Design Kit Daughter Card |

| DS21Q55 | Quad T1/E1/J1 Transceiver |

| DS21Q55N | Quad T1/E1/J1 Transceiver |

| DS21S07A | SCSI Terminator |

| DS21S07AE | Terminator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS21Q55 | 功能描述:IC TXRX QUAD T1/E1/J1 SCT 256BGA RoHS:否 類別:集成電路 (IC) >> 接口 - 電信 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS 產(chǎn)品變化通告:Product Discontinuation 06/Feb/2012 標(biāo)準(zhǔn)包裝:750 系列:* |

| DS21Q552 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 5V Quad T1 Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21Q552+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 5V Quad T1 Transceiver RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21Q552B | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS21Q552BN | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。