- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1915 > DS26900LN+ (Maxim Integrated Products)IC JTAG MUX/SWITCH 144-LQFP PDF資料下載

參數(shù)資料

| 型號(hào): | DS26900LN+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 3/49頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC JTAG MUX/SWITCH 144-LQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | * |

| 功能: | * |

| 電壓電源: | 單電源 |

| 電壓 - 電源,單路/雙路(±): | 3.14 V ~ 3.47 V |

| 電流 - 電源: | * |

| 工作溫度: | * |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-LQFP(20x20) |

| 包裝: | 托盤 |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

__________________________________________________________________________________________DS26900

11

NAME

PIN

TYPE

FUNCTION

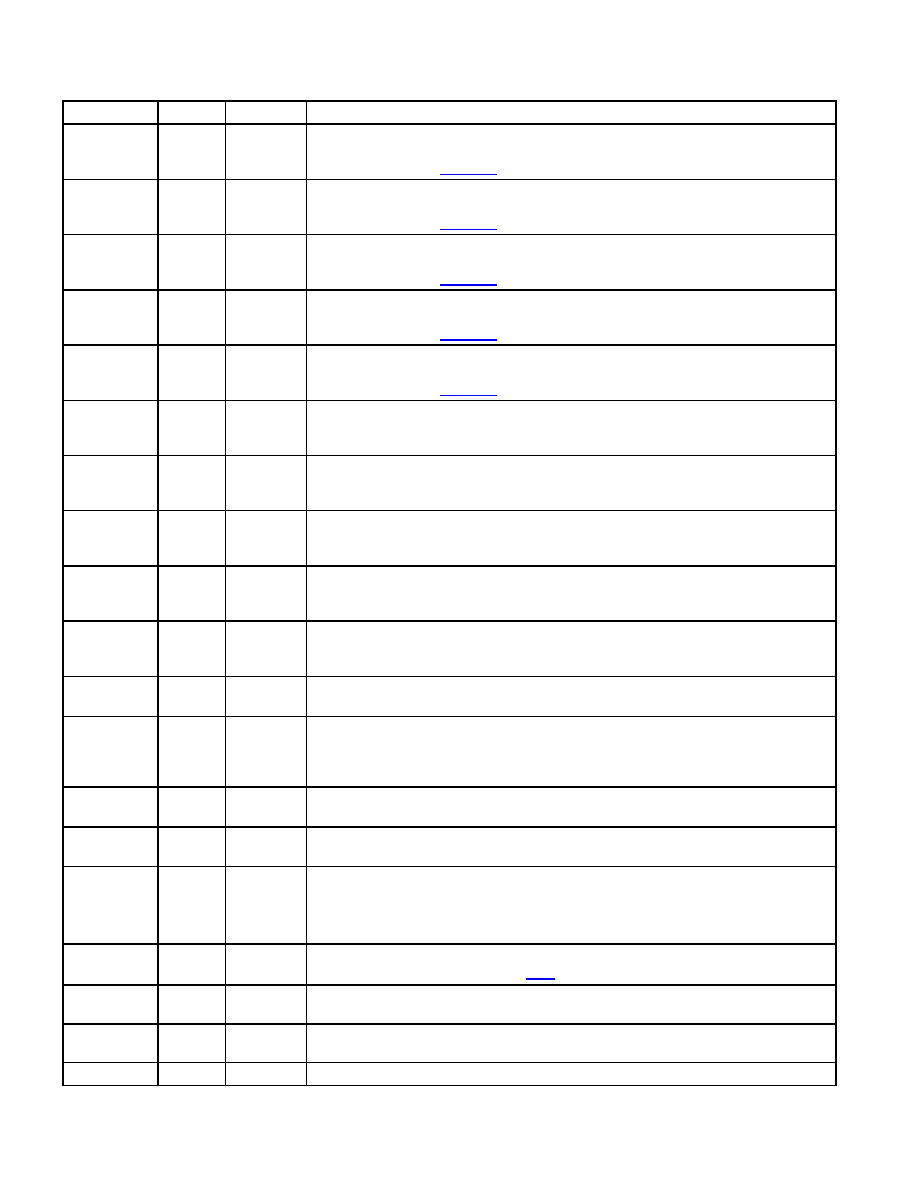

SSPI4

8

O

Selected Secondary Port Indicator Bit 4 (Active Low). Along with pins

SSPI3,

SSPI2, SSPI1, and SSPI0, this pin provides a hardware indication of the selected

secondary port. See Table 7-2 for more information.

SSPI3

9

O

Selected Secondary Port Indicator Bit 3 (Active Low). Along with pins

SSPI4,

SSPI2, SSPI1, and SSPI0, this pin provides a hardware indication of the selected

secondary port. See Table 7-2 for more information.

SSPI2

10

O

Selected Secondary Port Indicator Bit 2 (Active Low). Along with pins

SSPI4,

SSPI3, SSPI1, and SSPI0, this provides a hardware indication of the selected

secondary port. See Table 7-2 for more information.

SSPI1

11

O

Selected Secondary Port Indicator Bit 1 (Active Low). Along with pins

SSPI4,

SSPI3, SSPI2, and SSPI0, this pin provides a hardware indication of the selected

secondary port. See Table 7-2 for more information.

SSPI0

12

O

Selected Secondary Port Indicator Bit 0 (Active Low). Along with pins

SSPI4,

SSPI3, SSPI2, and SSPI1, this pin provides a hardware indication of the selected

secondary port. See Table 7-2 for more information.

GPIO[3]

14

Ipd/O

General-Purpose Input/Output Bit 3. (Internal 20k

Pulldown) This pin is a general-

purpose input/output, which can be read or driven via a register bit. This pin is in input

mode after a global reset.

GPIO[2]

15

Ipd/O

General-Purpose Input/Output Bit 2. (Internal 20k

Pulldown) This pin is a general-

purpose input/output, which can be read or driven via a register bit. This pin is in input

mode after a global reset.

GPIO[1]

16

Ipd/O

General-Purpose Input/Output Bit 1. (Internal 20k

Pulldown) This pin is a general-

purpose input/output, which can be read or driven via a register bit. This pin is in input

mode after a global reset.

GPIO[0]

17

Ipd/O

General-Purpose Input/Output Bit 0. (Internal 20k

Pulldown) This pin is a general-

purpose input/output, which can be read or driven via a register bit. This pin is in input

mode after a global reset.

RST

33

Ipu

Global Reset (Active Low). (Internal 10k

Pullup) A low state on this pin provides

an asynchronous reset for global registers and logic.

RST should be tied high for

normal operation.

TEST

62

Ipu

Test Enable (Active Low). (Internal 10k

Pullup) Factory test input. TEST must be

tied high or unconnected for normal operation.

HIZ

143

I

Output High-Impedance Enable (Active Low). When this pin is asserted low,

internal pullup and pulldown resistors are disabled, all outputs are put into high-

impedance mode, and master request inputs (

EREQ, TMREQ1, TMREQ2) are

disabled.

PTRST must also be asserted logic 0.

M[1]

141

Ipd

Mode Select Bit 1. (Internal 20k

Pulldown) Selects mode of operation of the device

(Single-Package, Cascade-Master, Cascade-Extension, or Deselect.

M[0]

142

Ipd

Mode Select Bit 0. (Internal 20k

Pulldown) Selects mode of operation of the device

(Single-Package, Cascade-Master, Cascade-Extension, or Deselect).

MCI

34

O

Master Conflict Indicator (Active Low). Indicates that more than one device is

requesting to be master.

Asserted low when more than one of the

EREQ, TMREQ1, or TMREQ2 signals is

asserted low.

DPDV

96

O

Deselected Port Data Value. This pin directly indicates the state of the DPDV bit in

the Device Configuration Register (DCR).

PTCK

40

I

Periphery JTAG Chain Test Clock. This input must be driven to a logic level during

normal operation.

PTDI

39

I

Periphery JTAG Chain Serial Data Input. This input must be driven to a logic level

during normal operation.

PTDO

38

O

Periphery JTAG Chain Serial Data Out

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS275E/T&R | IC TXRX LINE-PWR RS232 14-TSSOP |

| DS276S | IC TXRX LOW POWER RS-232 8-SOIC |

| DS2890P-000+T&R | IC POT DIGITAL 1-WIRE 100K 6TSOC |

| DS28CM00R-A00+T | IC SILICON SERIAL NUMBER SOT23-5 |

| DS30EA101SQE/NOPB | IC CABLE EQUALIZER 16LLP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS26900LN+ | 功能描述:多路器開關(guān) IC JTAG MUX RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 開關(guān)數(shù)量:4 開啟電阻(最大值):7 Ohms 開啟時(shí)間(最大值): 關(guān)閉時(shí)間(最大值): 傳播延遲時(shí)間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UQFN-16 |

| DS26900N+ | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:JTAG Multiplexer/Switch |

| DS26C31 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:CMOS QUAD TRI-STATE DIFFERENTIAL LINE DRIVER |

| DS26C31 DIE | 制造商:Texas Instruments 功能描述: |

| DS26C31_BBA3026X WAF | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。