- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384279 > EDD51321CBH-6CTT-E (ELPIDA MEMORY INC) 512M bits DDR SDRAM PDF資料下載

參數(shù)資料

| 型號: | EDD51321CBH-6CTT-E |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | 512M bits DDR SDRAM |

| 中文描述: | 16M X 32 SYNCHRONOUS DRAM, 5 ns, PBGA90 |

| 封裝: | ROHS COMPLIANT, FBGA-90 |

| 文件頁數(shù): | 5/55頁 |

| 文件大?。?/td> | 589K |

| 代理商: | EDD51321CBH-6CTT-E |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

EDD51321CBH

Preliminary Data Sheet E1094E30 (Ver. 3.0)

5

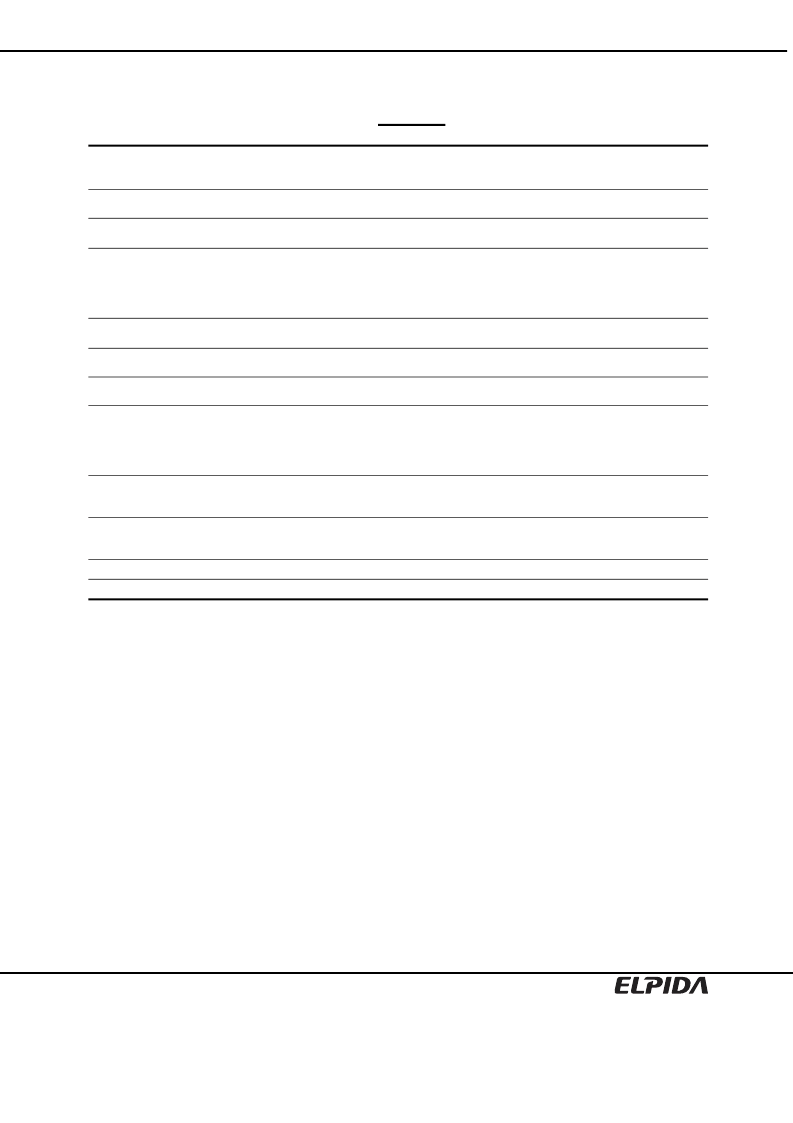

DC Characteristics 1 (TA = –20

°

C to +85

°

C, VDD and VDDQ = 1.8V +0.15V/–0.1V, VSS and VSSQ = 0V)

×

32

Parameter

Symbol

Grade

max.

Unit

Test condition

Notes

Operating current

IDD1

-6C

-7E

90

80

mA

Burst length = 2

tRC

≥

tRC (min.), IO = 0mA,

One bank active

CKE

≤

VIL (max.),

tCK = tCK (min.)

1

Standby current in power-down

IDD2P

3.0

mA

Standby current in power-down

(input signal stable)

IDD2PS

2.8

mA

CKE

≤

VIL (max.), tCK =

∞

Standby current in non power-down

IDD2N

6.0

mA

CKE

≥

VIH (min.),

tCK = tCK (min.),

/CS

≥

VIH (min.),

Input signals are changed one time

during 2tCK.

CKE

≥

VIH (min.), tCK =

∞

,

Input signals are stable.

CKE

≤

VIL (max.),

tCK = tCK (min.)

Standby current in non power-down

(input signal stable)

IDD2NS

4.0

mA

Active standby current in power-down IDD3P

5.0

mA

Active standby current in power-down

(input signal stable)

IDD3PS

4.0

mA

CKE

≤

VIL (max.), tCK =

∞

Active standby current in non power-

down

IDD3N

10

mA

CKE

≥

VIH (min.),

tCK = tCK (min.),

/CS

≥

VIH (min.),

Input signals are changed one time

during 2 tCK.

Active standby current in non power-

down

(input signal stable)

IDD3NS

7.0

mA

CKE

≥

VIH (min.), tCK =

∞

,

Input signals are stable.

Burst operating current

IDD4

-6C

-7E

150

120

mA

Burst length = 4

tCK

≥

tCK (min.),

IOUT = 0mA, All banks active

tRFC

≥

tRFC (min.)

2

Refresh current

IDD5

90

mA

3

Self-refresh current

IDD6

3.5

mA

CKE

≤

0.2V

Notes: 1. IDD1 depends on output loading and cycle rates. Specified values are obtained with the output open.

In addition to this, IDD1 is measured on condition that addresses are changed only one time during

tCK (min.).

2. IDD4 depends on output loading and cycle rates. Specified values are obtained with the output open.

In addition to this, IDD4 is measured on condition that addresses are changed only one time during

tCK (min.).

3. IDD5 is measured on condition that addresses are changed only one time during tCK (min.).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EDD51321CBH-7ETT-E | 512M bits DDR SDRAM |

| EDE1116ABSE-6E-E | 1G bits DDR2 SDRAM |

| EDE1104ABSE | 1G bits DDR2 SDRAM |

| EDE1104ABSE-4A-E | 1G bits DDR2 SDRAM |

| EDE1104ABSE-5C-E | 1G bits DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EDD51321CBH-7ETT-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR SDRAM |

| EDD51321DBH-5BTS-F | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR Mobile RAM? WTR (Wide Temperature Range) |

| EDD51321DBH-6ETS-F | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR Mobile RAM? WTR (Wide Temperature Range) |

| EDD51321DBH-TS | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR Mobile RAM? WTR (Wide Temperature Range) |

| EDD51323DBH-5BLS-F | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:512M bits DDR Mobile RAM? WTR (Wide Temperature Range), Low Power Function |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。