- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1931 > KSZ8842-PMBL AM TR (Micrel Inc)IC ETHERNET SW 2PORT 100LFBGA PDF資料下載

參數(shù)資料

| 型號(hào): | KSZ8842-PMBL AM TR |

| 廠商: | Micrel Inc |

| 文件頁(yè)數(shù): | 30/119頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC ETHERNET SW 2PORT 100LFBGA |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 控制器類型: | 以太網(wǎng)開關(guān)控制器 |

| 接口: | PCI |

| 電源電壓: | 3.1 V ~ 3.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LFBGA |

| 供應(yīng)商設(shè)備封裝: | 100-LFBGA |

| 包裝: | 帶卷 (TR) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)

Micrel, Inc.

KSZ8842-PMQL/PMBL

October 2007

18

M9999-100207-1.5

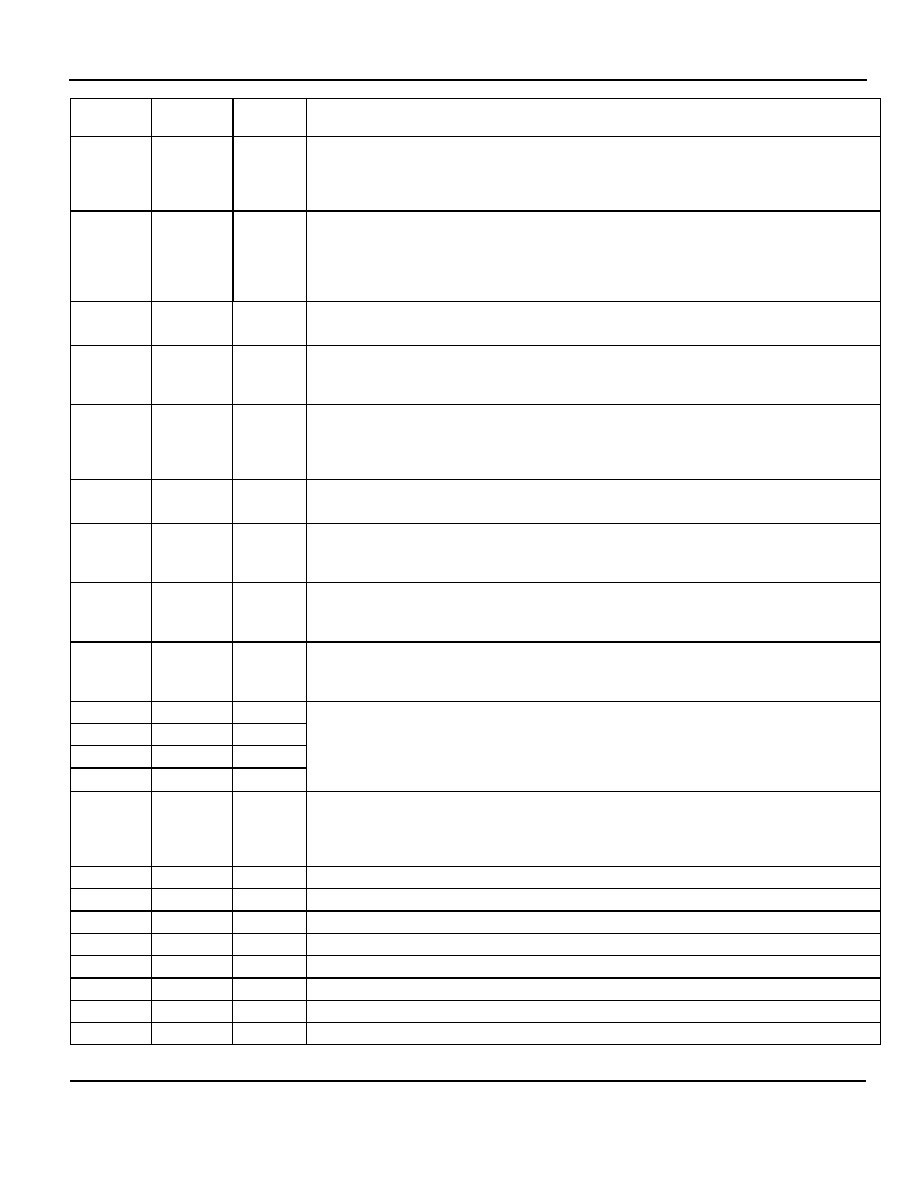

Ball

Number

Ball

Name

Type

Ball Function

K2

IRDYN

I/O

PCI Initiator Ready

As a bus master, this signal is asserted low to indicate valid data phases on PAD [31:0]

during write data phases, indicates it is ready to accept data during read data phases. As a

target, it’ll monitor this IRDYN signal that indicates the master has put the data on the bus.

H3

TRDYN

I/O

PCI Target Ready

As a bus target, this signal is asserted low to indicate valid data phases on PAD [31:0] during

read data phases, indicating it is ready to accept data during write data phases. As a master,

it will monitor this TRDYN signal that indicates the target is ready for data during read/write

operation.

J3

STOPN

I/O

PCI Stop

This signal is asserted low by the target device to stop the current transaction

K3

IDSEL

I/O

PCI Initialization Device Select.

This signal is used to select the KSZ8842-PMQL/PMBL during configuration read and write

transactions.

H4

DEVSELN

I/O

PCI Device Select

This signal is asserted low when it is selected as a target during a bus transaction. As a bus

master, the KSZ8842-PMBL samples this signal to insure that the destination address for the

data transfer is recognized by a PCI target.

J4

REQN

O

PCI Request

The KSZ8842-PMBL will assert this signal low to request PCI bus master operation.

K4

GNTN

I

PCI Grant

This signal is asserted low to indicate to the KSZ8842-PMBL that it has been granted the PCI

bus master operation.

H5

PERRN

I/O

PCI Parity Error

The KSZ8842-PMBL as a master or target will assert this signal low to indicate a parity error

on any incoming data. As a bus master, it will monitor this signal on all write operations.

J5

SERRN

O

PCI System Error

This system error signal is asserted low by the KSZ8842-PMBL.This signal is used to report

address parity errors.

K5

CBE3N

I

K6

CBE2N

I

J6

CBE1N

I

H6

CBE0N

I

Command and Byte Enable

These signals are multiplexed on the same PCI pins. During the address phase, these lines

define the bus command. During the data phase, these lines are used as Byte Enables. The

Byte enables are valid for the entire data phase and determine which byte lanes carry

meaningful data.

K7

PAD31

I/O

PCI Address / Data 31

Address and data are multiplexed on the all of the PAD balls. The PAD pins carry the

physical address during the first clock cycle of a transaction, and carry data during the

subsequent clock cycles.

J7

PAD30

I/O

PCI Address / Data 30

H7

PAD29

I/O

PCI Address / Data 29

K8

PAD28

I/O

PCI Address / Data 28

J8

PAD27

I/O

PCI Address / Data 27

H8

PAD26

I/O

PCI Address / Data 26

K9

PAD25

I/O

PCI Address / Data 25

J9

PAD24

I/O

PCI Address / Data 24

K10

PAD23

I/O

PCI Address / Data 23

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KSZ8842-PMQLI | IC ETHERNET SW 2PORT PCI 128PQFP |

| KSZ8851-16MLLI TR | IC MAC CTLR 1PORT W/BUS 48LQFP |

| KSZ8851-16MLLJ | IC CTLR MAC 1PORT NON-PCI 48LQFP |

| KSZ8851-32MQLI | IC CTLR MAC/PHY NON PCI 128PQFP |

| KSZ8851-32MQL | IC CTLR MAC/PHY NON PCI 128PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KSZ8842-PMBL-EVAL | 功能描述:以太網(wǎng)開發(fā)工具 2+1 Port 10/100 Ethernet Switch with 32b/33MHz PCI Interface (BGA Version) Eval Board RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

| KSZ8842-PMBL-TR | 功能描述:Ethernet Switch 10/100 Base-T/TX PHY PCI Interface 100-LFBGA (9x9) 制造商:microchip technology 系列:- 包裝:剪切帶(CT) 零件狀態(tài):停產(chǎn) 協(xié)議:以太網(wǎng) 功能:開關(guān) 接口:PCI 標(biāo)準(zhǔn):10/100 Base-T/TX PHY 電壓 - 電源:3.1 V ~ 3.5 V 電流 - 電源:122mA 工作溫度:-40°C ~ 85°C 封裝/外殼:100-LFBGA 供應(yīng)商器件封裝:100-LFBGA(9x9) 標(biāo)準(zhǔn)包裝:1 |

| KSZ8842-PMQL | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI bus interface(Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| KSZ8842-PMQL-EVAL | 功能描述:以太網(wǎng)開發(fā)工具 KSZ8842-PMQL Evaluation Board RoHS:否 制造商:Micrel 產(chǎn)品:Evaluation Boards 類型:Ethernet Transceivers 工具用于評(píng)估:KSZ8873RLL 接口類型:RMII 工作電源電壓: |

| KSZ8842-PMQLI | 功能描述:以太網(wǎng) IC 2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI bus interface, Ind Temp (Lead Free) RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。