- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358741 > LAN9116 (SMSC Corporation) Highly Efficient Single-Chip 10/100 Non-PCI Ethernet Controller PDF資料下載

參數(shù)資料

| 型號: | LAN9116 |

| 廠商: | SMSC Corporation |

| 英文描述: | Highly Efficient Single-Chip 10/100 Non-PCI Ethernet Controller |

| 中文描述: | 高效的單芯片10/100非PCI以太網(wǎng)控制器 |

| 文件頁數(shù): | 78/126頁 |

| 文件大小: | 831K |

| 代理商: | LAN9116 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁當前第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁

Highly Efficient Single-Chip 10/100 Non-PCI Ethernet Controller

Datasheet

Revision 1.1 (05-17-05)

78

SMSC LAN9116

DATASHEET

In addition to the host-accessible FIFOs, the MAC Interface Layer (MIL) contains an additional 2K

bytes of TX, and 128 bytes of RX FIFO buffering. These sizes are fixed, and cannot be adjusted by

the host.

As space in the TX MIL (Mac Interface Layer) FIFO frees, data is moved into it from the TX data FIFO.

Depending on the size of the frames to be transmitted, the MIL can hold up to two Ethernet frames.

This is in addition to any TX data that may be queued in the TX data FIFO.

Conversely, as data is received by the LAN9116, it is moved from the MAC to the RX MIL FIFO, and

then into the RX data FIFO. When the RX data FIFO fills up, data will continue to collect in the RX

MIL FIFO. If the RX MIL FIFO fills up and overruns, subsequent RX frames will be lost until room is

made in the RX data FIFO. For each frame of data that is lost, the RX Dropped Frames Counter

(RX_DROP) is incremented.

RX and TX MIL FIFO levels are not visible to the host processor. RX and TX MIL FIFOs operate

independent of the TX adatand RX data and status FIFOs. FIFO levels set for the RX and TX data

and Status FIFOs do not take into consideration the MIL FIFOs.

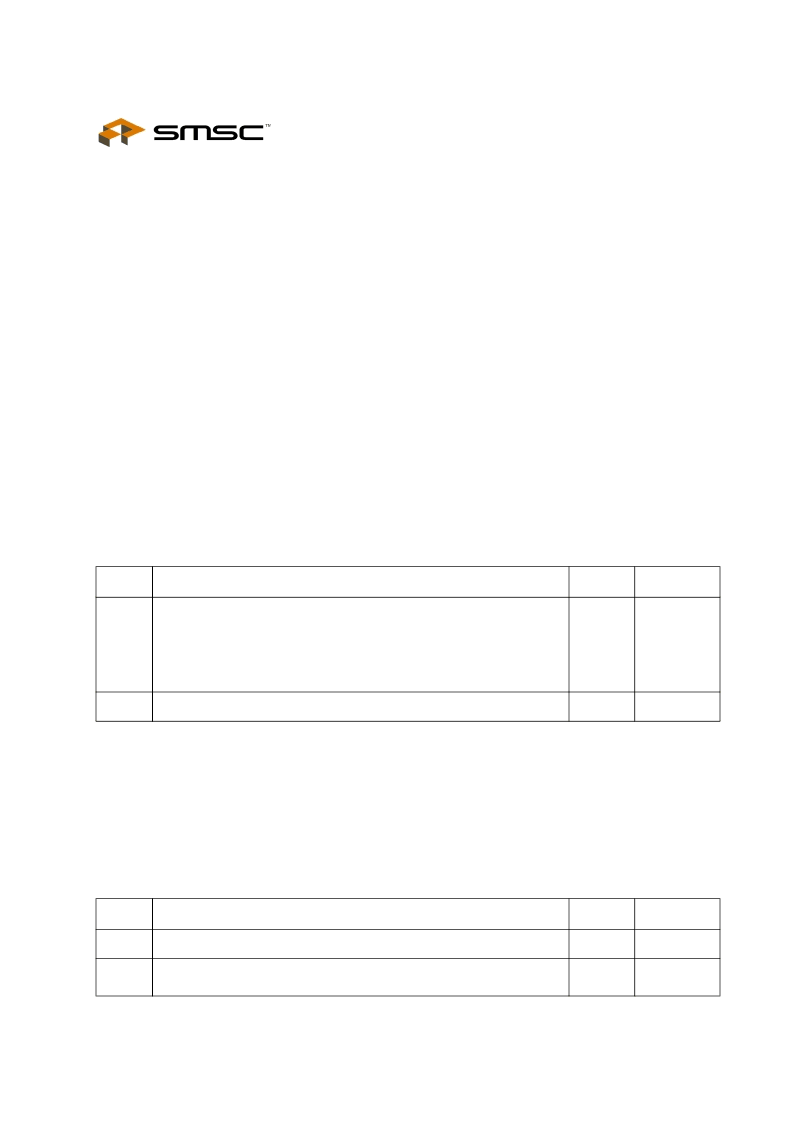

5.3.10

RX_DP_CTRL—Receive Datapath Control Register

This register is used to discard unwanted receive frames.

5.3.11

RX_FIFO_INF—Receive FIFO Information Register

This register contains the used space in the receive FIFOs of the LAN9116 Ethernet Controller.

Offset:

78h

Size:

32 bits

BITS

DESCRIPTION

TYPE

DEFAULT

31

RX Data FIFO Fast Forward (RX_FFWD):

Writing a ‘1’ to this bit causes

the RX data FIFO to fast-forward to the start of the next frame. This bit will

remain high until the RX data FIFO fast-forward operation has completed.

No reads should be issued to the RX data FIFO while this bit is high.

Note:

Please refer to section “Receive Data FIFO Fast Forward” on

page 53 for detailed information regarding the use of RX_FFWD.

R/W

0h

30-0

Reserved

RO

-

Offset:

7Ch

Size:

32 bits

BITS

DESCRIPTION

TYPE

DEFAULT

31-24

Reserved

RO

-

23-16

RX Status FIFO Used Space (RXSUSED).

Indicates the amount of space

in DWORDs, used in the RX Status FIFO.

RO

00h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN9117 | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| LAN9117-MD | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| LAN9117-MT | HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| LAN9118 | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

| LAN9118-MD | HIGH PERFORMANCE SINGLE CHIP 10/100NON PCI ETHERNET CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN9116-MD | 功能描述:以太網(wǎng) IC Efficient Sngl Chip 10/100 Ethrnt RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN9116-MT | 功能描述:以太網(wǎng) IC Ethernet IC 32bit Superior Perf RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN9117 | 制造商:SMSC 制造商全稱:SMSC 功能描述:HIGH PERFORMANCE SINGLE-CHIP 10/100 NON-PCI ETHERNET CONTROLLER |

| LAN9117-MD | 功能描述:以太網(wǎng) IC HiPerfrm Sngl-Chip 10/100 Ethrnt RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| LAN9117-MT | 功能描述:以太網(wǎng) IC HiPerfrm Sngl-Chip 10/100 Ethrnt RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。