- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378045 > PCI1221GHK (Texas Instruments, Inc.) KPT 11C 11#16 SKT PLUG PDF資料下載

參數(shù)資料

| 型號(hào): | PCI1221GHK |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | KPT 11C 11#16 SKT PLUG |

| 中文描述: | PC卡控制器 |

| 文件頁(yè)數(shù): | 46/123頁(yè) |

| 文件大小: | 1659K |

| 代理商: | PCI1221GHK |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

PCI1221 GHK/PDV

PC CARD CONTROLLERS

SCPS042 – JULY 1998

46

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

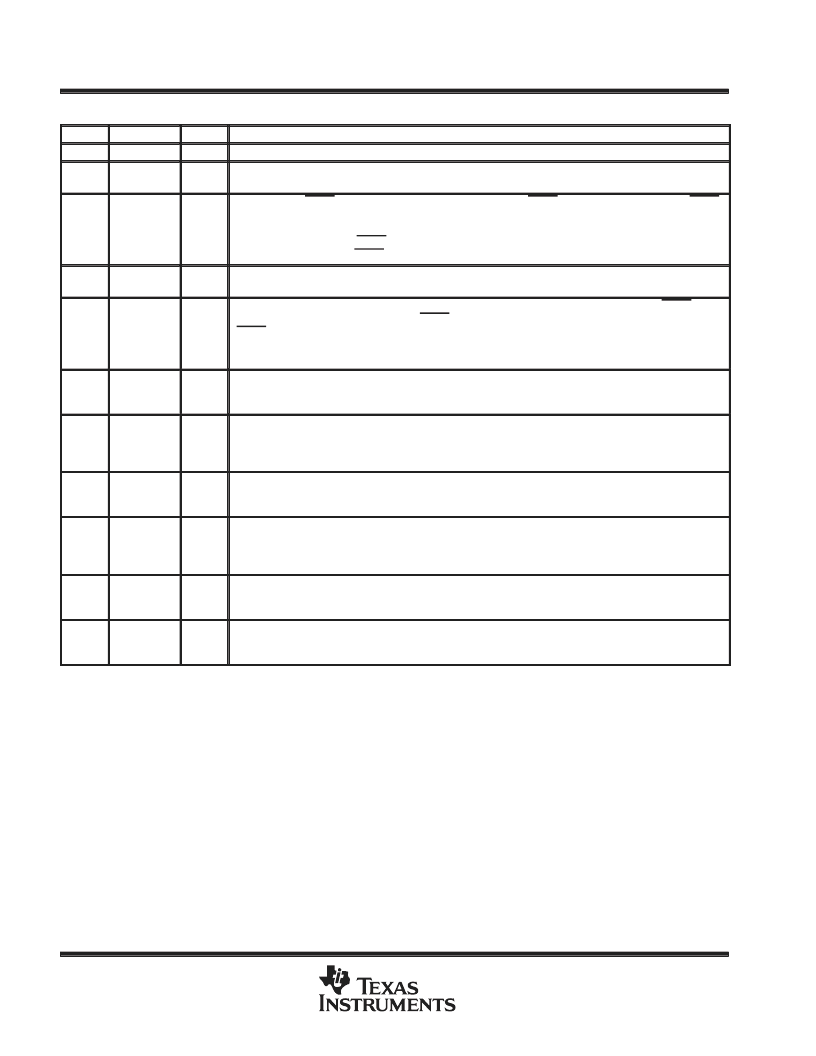

Table 16. Command Register

BIT

SIGNAL

TYPE

FUNCTION

15–10

RSVD

R

Reserved. Bits 15–10 are read only and return 0s when read. Write transactions have no effect.

9

FBB_EN

R

Fast back-to-back enable. The PCI1221 does not generate fast back-to-back transactions; therefore, bit

9 is read only and returns 0s when read.

8

SERR_EN

R/W

System Error (SERR) enable. Bit 8 controls the enable for the SERR driver on the PCI interface. SERR

can be asserted after detecting an address parity error on the PCI bus. Both bit 8 and bit 6 must be set

for the PCI1221 to report address parity errors.

0 = Disable SERR output driver (default)

1 = Enable SERR output driver

7

STEP_EN

R

Address/data stepping control. The PCI1221 does not support address/data stepping, and bit 7 is

hardwired to 0. Write transactions to this bit have no effect.

6

PERR_EN

R/W

Parity error response enable. Bit 6 controls the PCI1221’s response to parity errors through PERR. Data

parity errors are indicated by asserting PERR, whereas address parity errors are indicated by asserting

SERR.

0 = PCI1221 ignores detected parity error (default)

1 = PCI1221 responds to detected parity errors

5

VGA_EN

R

VGA palette snoop. Bit 5 controls how PCI devices handle accesses to video graphics array (VGA) palette

registers. The PCI1221 does not support VGA palette snooping; therefore, this bit is hardwired to 0. Bit

5 is read only and returns 0 when read. Write transactions to this bit have no effect.

4

MWI_EN

R

Memory write and invalidate enable. Bit 4 controls whether a PCI initiator device can generate memory

write and Invalidate commands. The PCI1221 controller does not support memory write and invalidate

commands, it uses memory write commands instead; therefore, this bit is hardwired to 0. Bit 4 is read only

and returns 0 when read. Write transactions to this bit have no effect.

3

SPECIAL

R

Special cycles. Bit 3 controls whether or not a PCI device ignores PCI special cycles. The PCI1221 does

not respond to special cycle operations; therefore, this bit is hardwired to 0. Bit 3 is read only and returns

0 when read. Write transactions to this bit have no effect.

2

MAST_EN

R/W

Bus master control. Bit 2 controls whether or not the PCI1221 can act as a PCI bus initiator (master). The

PCI1221 can take control of the PCI bus only when this bit is set.

0 = Disables the PCI1221’s ability to generate PCI bus accesses (default)

1 = Enables the PCI1221’s ability to generate PCI bus accesses

1

MEM_EN

R/W

Memory space enable. Bit 1 controls whether or not the PCI1221 can claim cycles in PCI memory space.

0 = Disables the PCI1221’s response to memory space accesses (default)

1 = Enables the PCI1221’s response to memory space accesses

0

IO_EN

R/W

I/O space control. Bit 0 controls whether or not the PCI1221 can claim cycles in PCI I/O space.

0 = Disables the PCI1221 from responding to I/O space accesses (default)

1 = Enables the PCI1221 to respond to I/O space accesses

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI1410GHK | PC CARD CONTROLLERS |

| PCI1510GVF | PC CARD CONTROLLERS |

| PCI1510ZVF | PC CARD CONTROLLERS |

| PCI1520I | PC CARD CONTROLLERS |

| PCI4410A | PC CARD AND OHCI CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI1221PDV | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| PCI1225 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:PC CARD CONTROLLERS |

| PCI1225GHK | 制造商:Texas Instruments 功能描述: |

| PCI1225PDV | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| PCI-1240U | 制造商:ADVANTECH 制造商全稱:Advantech Co., Ltd. 功能描述:4-axis Stepping and Servo Motor Control Universal PCI Card |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。