- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367908 > pentium II (Intel Corp.) pentium II processor With On-die Cache Mobile Module Connector 1 (MMC-1)(帶緩存和連接器1的奔II處理器) PDF資料下載

參數(shù)資料

| 型號: | pentium II |

| 廠商: | Intel Corp. |

| 英文描述: | pentium II processor With On-die Cache Mobile Module Connector 1 (MMC-1)(帶緩存和連接器1的奔II處理器) |

| 中文描述: | 奔騰II處理器芯片上緩存手機(jī)模塊連接器1(MMC管理- 1)(帶緩存和連接器1的奔二處理器) |

| 文件頁數(shù): | 11/34頁 |

| 文件大小: | 582K |

| 代理商: | PENTIUM II |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

11

Intel

a

Pentium

a

II Processor With On-die Cache Mobile Module MMC-1

3.1.4

Processor and PIIX4E/M Sideband (9

Signals)

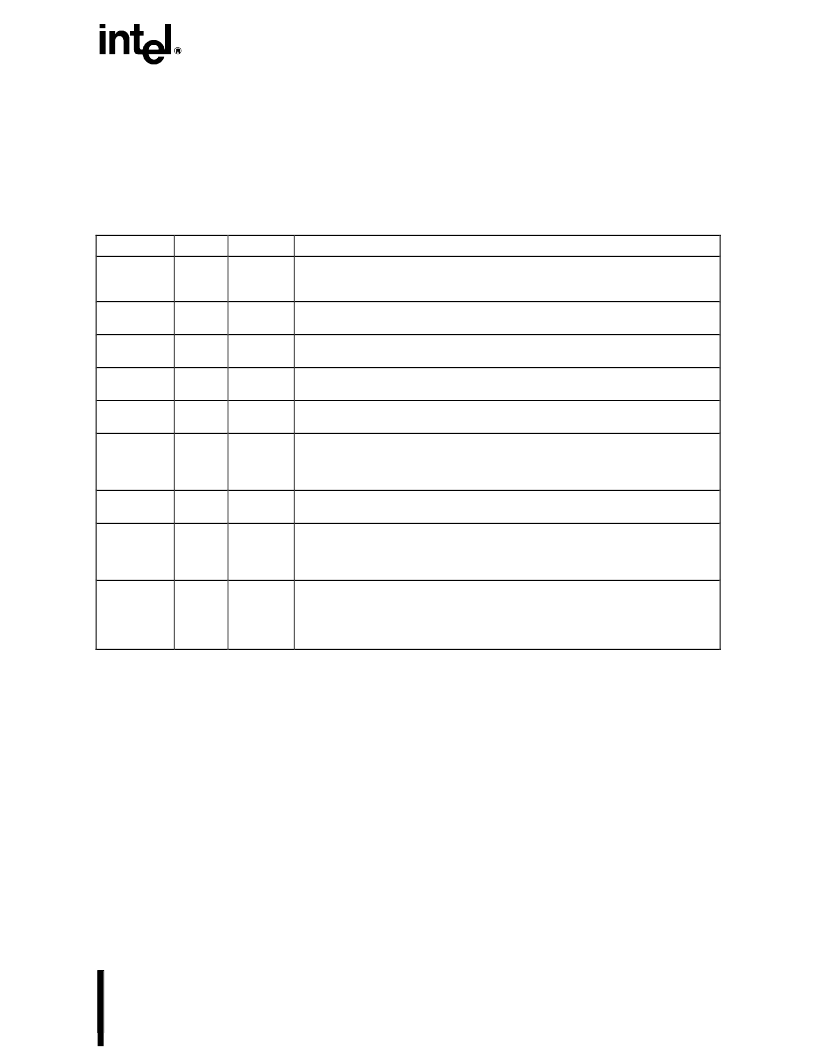

Table 4 lists the processor and PIIX4E/M sideband interface

signals. The voltage level for these signals is determined by

V_CPUIO.

Table 4. Processor/PIIX4E/M Sideband Signal Descriptions

Voltage

Description

Name

Type

FERR#

O

CMOS

V_CPUIO

Numeric Coprocessor Error:

This pin functions as a FERR# signal supporting

coprocessor errors. This signal is tied to the coprocessor error signal on the processor

and is driven by the processor to the PIIX4E/M.

CPURST

N/C

CMOS

ID

CMOS

ID

CMOS

ID

CMOS

ID

CMOS

V_CPUIO

Processor Reset:

The signal is not used on the module.

IGNNE#

V_CPUIO

Ignore Error:

This open-drain signal is connected to the Ignore Error pin on the

processor and is driven by the PIIX4E/M.

INIT#

V_CPUIO

Initialization:

INIT# is asserted by the PIIX4E/M to the processor for system

initialization. This signal is an open-drain.

INTR

V_CPUIO

Processor Interrupt:

INTR is driven by the PIIX4E/M to signal the processor that an

interrupt request is pending and needs to be serviced. This signal is an open-drain.

NMI

V_CPUIO

Non-Maskable Interrupt:

NMI is used to force a non-maskable interrupt to the

processor.

The PIIX4E/M ISA bridge generates NMI when either SERR# or IOCHK# is

asserted, depending on how the NMI Status and Control Register is programmed. This

signal is an open-drain.

A20M#

ID

CMOS

ID

CMOS

V_CPUIO

Address Bit 20 Mask:

When enabled, this open-drain signal causes the processor to

emulate the address wraparound at 1 MB, which occurs on the Intel 8086 processor.

SMI#

V_CPUIO

System Management Interrupt:

SMI# is an active low synchronous output from the

PIIX4E/M that is asserted in response to one of many enabled hardware or software

events.

The SMI# open-drain signal can be an asynchronous input to the processor.

However, in this chip set SMI# is synchronous to PCLK.

STPCLK#

ID

CMOS

V_CPUIO

Stop Clock:

STPCLK# is an active low synchronous open-drain output from the

PIIX4E/M that is asserted in response to one of many hardware or software events.

STPCLK# connects directly to the processor and is synchronous to PCICLK.

When the

processor samples STPCLK# asserted, it responds by entering a low power state (Quick

Start). The processor will only exit this mode when this signal is deasserted.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PERICOMPI7C8150 | 2-Port PCI-to-PCI Bridge |

| PESDXL2BT | Low capacitance double bidirectional ESD protection diodes in SOT23 |

| PESDXL2UM | LJT 23C 21#20 2#16 PIN RECP |

| PETAM1270BK300R | BRAID SLEEVING 300M |

| PETAM1270BK50C | 5V RS232 Transceiver with One Receiver Active in SHUTDOWN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。