- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373275 > RK80530KZ017512 MICROPROCESSOR|32-BIT|CMOS|PGA|370PIN|CERAMIC PDF資料下載

參數(shù)資料

| 型號(hào): | RK80530KZ017512 |

| 英文描述: | MICROPROCESSOR|32-BIT|CMOS|PGA|370PIN|CERAMIC |

| 中文描述: | 微處理器| 32位|的CMOS |美巡賽| 370PIN |陶瓷 |

| 文件頁數(shù): | 77/86頁 |

| 文件大?。?/td> | 882K |

| 代理商: | RK80530KZ017512 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當(dāng)前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

Datasheet

77

Intel

Pentium

III Processor with 512KB L2 Cache at 1.13GHz to 1.40GHz

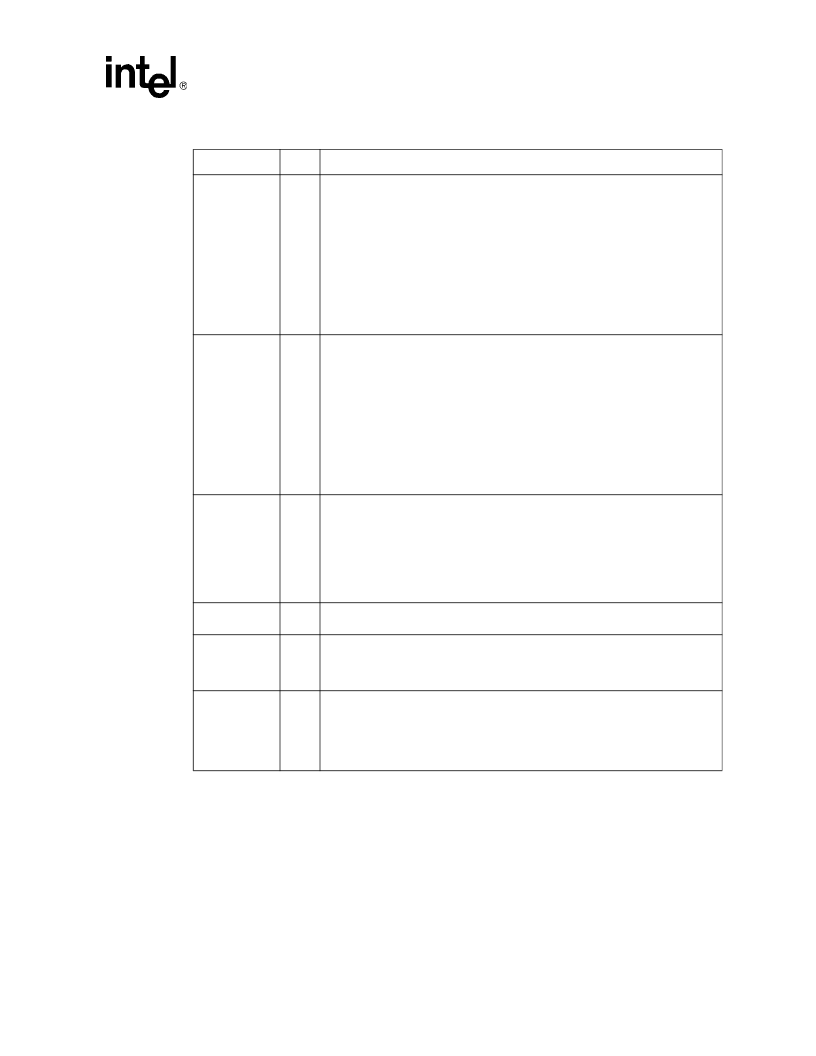

BERR#

I/O

The BERR# (Bus Error) signal is asserted to indicate an unrecoverable error

without a bus protocol violation. It may be driven by all processor system bus

agents, and must connect the appropriate pins of all such agents, if used. However,

Intel Pentium III processors do not observe assertions of the BERR# signal.

BERR# assertion conditions are configurable at a system level. Assertion options

are defined by the following options:

Enabled or disabled.

Asserted optionally for internal errors along with IERR#.

Asserted optionally by the request initiator of a bus transaction after it observes

an error.

Asserted by any bus agent when it observes an error in a bus transaction.

BINIT#

I/O

The BINIT# (Bus Initialization) signal may be observed and driven by all processor

system bus agents, and if used must connect the appropriate pins of all such

agents. If the BINIT# driver is enabled during power on configuration, BINIT# is

asserted to signal any bus condition that prevents reliable future information.

If BINIT# observation is enabled during power-on configuration, and BINIT# is

sampled asserted, all bus state machines are reset and any data which was in

transit is lost. All agents reset their rotating ID for bus arbitration to the state after

Reset, and internal count information is lost. The L1 and L2 caches are not

affected.

If BINIT# observation is disabled during power-on configuration, a central agent

may handle an assertion of BINIT# as appropriate to the error handling architecture

of the system.

BNR#

I/O

The BNR# (Block Next Request) signal is used to assert a bus stall by any bus

agent who is unable to accept new bus transactions. During a bus stall, the current

bus owner cannot issue any new transactions.

Since multiple agents might need to request a bus stall at the same time, BNR# is a

wire-OR signal which must connect the appropriate pins of all processor system

bus agents. In order to avoid wire-OR glitches associated with simultaneous edge

transitions driven by multiple drivers, BNR# is activated on specific clock edges and

sampled on specific clock edges.

BP[3:2]#

I/O

The BP[3:2]# (Breakpoint) signals are outputs from the processor that indicate the

status of breakpoints.

BPM[1:0]#

I/O

The BPM[1:0]# (Breakpoint Monitor) signals are breakpoint and performance

monitor signals. They are outputs from the processor which indicate the status of

breakpoints and programmable counters used for monitoring processor

performance.

BPRI#

I

The BPRI# (Bus Priority Request) signal is used to arbitrate for ownership of the

processor system bus. It must connect the appropriate pins of all processor system

bus agents. Observing BPRI# active (as asserted by the priority agent) causes all

other agents to stop issuing new requests, unless such requests are part of an

ongoing locked operation. The priority agent keeps BPRI# asserted until all of its

requests are completed, then releases the bus by deasserting BPRI#.

Table 39. Signal Description (Sheet 2 of 9)

Name

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RK80532PC041512 | Microprocessor |

| RK9410 | TRANSISTOR | MOSFET | N-CHANNEL | 30V V(BR)DSS | 7A I(D) | SO |

| RKC-SERIES | Interface IC |

| RKCB-SERIES | Interface IC |

| RKCR-SERIES | Interface IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RK80530KZ017512S L5XL | 制造商:Intel 功能描述:32BIT MPU 80530KZ017512 1.40G |

| RK80530KZ017512S L6BY | 制造商:Intel 功能描述:MPU Pentium 制造商:Intel 功能描述:MPU Pentium? III Processor-S 64-Bit 0.13um 1.4GHz 370-Pin FCPGA2 |

| RK80530PZ001256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| RK80530PZ006256 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| RK80530PZ009256 | 制造商:Rochester Electronics LLC 功能描述:PIII 1.2G 256 ON DIE CACHE FC-PGA2 - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。