- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376314 > rosa51 (SIEMENS AG) MultiMediaCard Adapter(多媒體卡適配器) PDF資料下載

參數(shù)資料

| 型號: | rosa51 |

| 廠商: | SIEMENS AG |

| 英文描述: | MultiMediaCard Adapter(多媒體卡適配器) |

| 中文描述: | 多媒體卡(多媒體卡適配器) |

| 文件頁數(shù): | 41/54頁 |

| 文件大小: | 510K |

| 代理商: | ROSA51 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

526$

&RQILJXUDWLRQ

Siemens AG Semiconductors

Version 5.2

Confidential

20/10/1998

41

This register controls the interrupt handling of the interrupt sources in the Adapter Status, CIM Sta-

tus and MultiMediaCard Status registers.

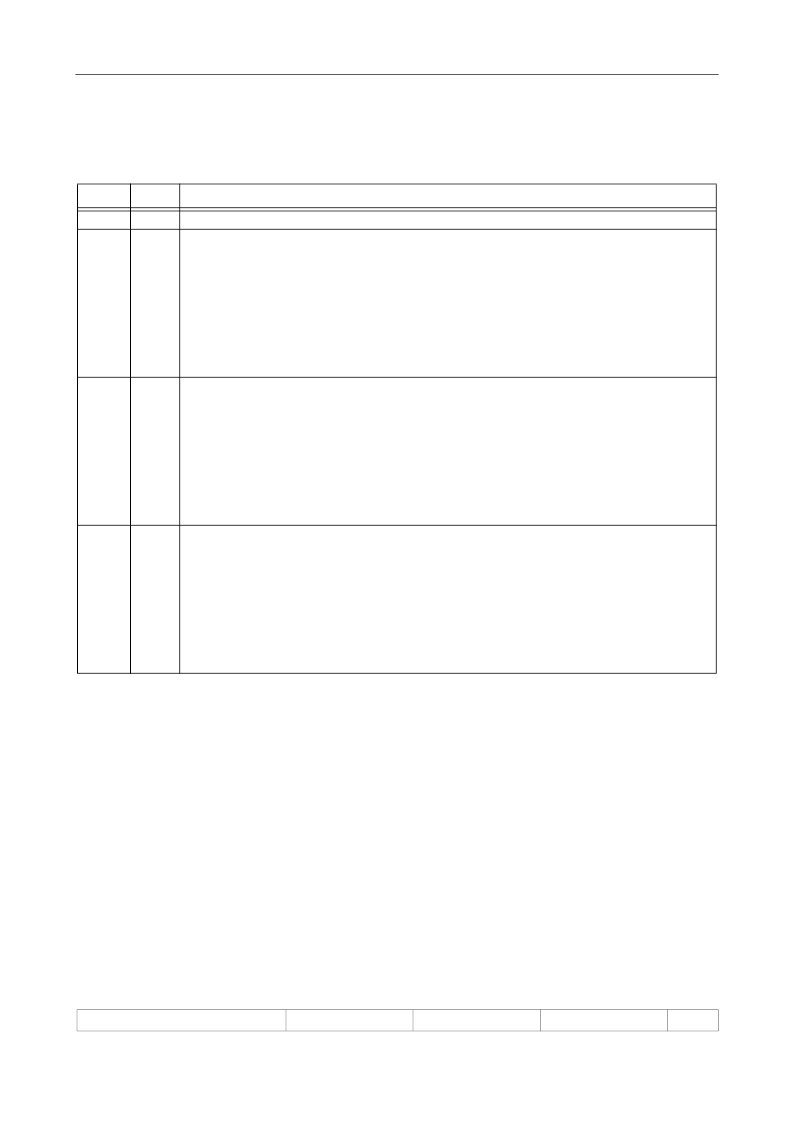

%LW

7\SH

'HVFULSWLRQ

39:0

39:16

W

W

This register can be written by the CAM_SET_IRQMASK command

00&0DVN

- MultiMediaCard status interrupt enable.

Each bit enables an interrupt source in the

00&6WDWXV

register. When enabled, each

positive edge of the corresponding card status input will generate an interrupt request on

the application interface

,54B1

output pin.

When disabled, the MultiMediaCard status register continues to reflect the correspond-

ing interrupt sources.

‘1’ - interrupt source enabled,

‘0’ - interrupt source disabled.

0x000000 (default value).

&LP0DVN

- Macro status interrupt enable.

Each bit enables an interrupt source in the

&LP6WDWXV

register. When enabled, each

positive edge of the corresponding macro command status input will generate an inter-

rupt request on the application interface

,54B1

output pin.

When disabled, the

&LP6WDWXV

register continues to reflect the corresponding interrupt

sources.

‘1’ - interrupt source enabled,

‘0’ - interrupt source disabled.

0x00 (default value).

$GD0DVN

- Adapter status interrupt enable.

Each bit enables an interrupt source in the

$GD6WDWXV

register. When enabled, each

positive edge of the corresponding adapter status input will generate an interrupt request

on the application interface

,54B1

output pin.

When disabled, the adapter status register continues to reflect the corresponding inter-

rupt sources.

‘1’ - interrupt source enabled,

‘0’ - interrupt source disabled.

0x00 (default value).

15:8

W

7:0

W

7DEOH,540DVNUHJLVWHU

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ROSE-1 | FREQUENCY MIXERS |

| ROSE-2 | FREQUENCY MIXERS |

| ROSE-50 | SMB Termination |

| RP-12C | mask-diffused gaasp led |

| RP05-4824DE | POWERLINE - DC/DC - CONVERTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ROSE1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| ROSE-1 | 制造商:MINI 制造商全稱:Mini-Circuits 功能描述:FREQUENCY MIXERS |

| ROSE2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| ROSE-2 | 制造商:MINI 制造商全稱:Mini-Circuits 功能描述:FREQUENCY MIXERS |

| ROSE-50 | 制造商:MINI 制造商全稱:Mini-Circuits 功能描述:SMB Termination |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。