- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371179 > T7507 T7507 Quad PCM Codec with Filters, Termination Impedance, and Hybrid Balance PDF資料下載

參數(shù)資料

| 型號: | T7507 |

| 元件分類: | Codec |

| 英文描述: | T7507 Quad PCM Codec with Filters, Termination Impedance, and Hybrid Balance |

| 中文描述: | T7507四路PCM編解碼器與過濾器,終端阻抗,以及混合平衡 |

| 文件頁數(shù): | 8/30頁 |

| 文件大?。?/td> | 558K |

| 代理商: | T7507 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

8

Lucent Technologies Inc.

Data Sheet

August 1999

Termination Impedance, and Hybrid Balance

T7507 Quad PCM Codec with Filters,

Functional Description

(continued)

PCM Interface

(continued)

The entire device is placed in a powerdown mode if

FSEP remains low for 500 μs. Powerdown is not guar-

anteed if MCLK is lost unless the device is already in

the powerdown mode due to FSEP low for at least

500 μs.

The T7507 also offers an output pin, DxEN. This pin is

an open-drain output that pulses low during the period

when the D

X

output is enabled.

Analog Interface

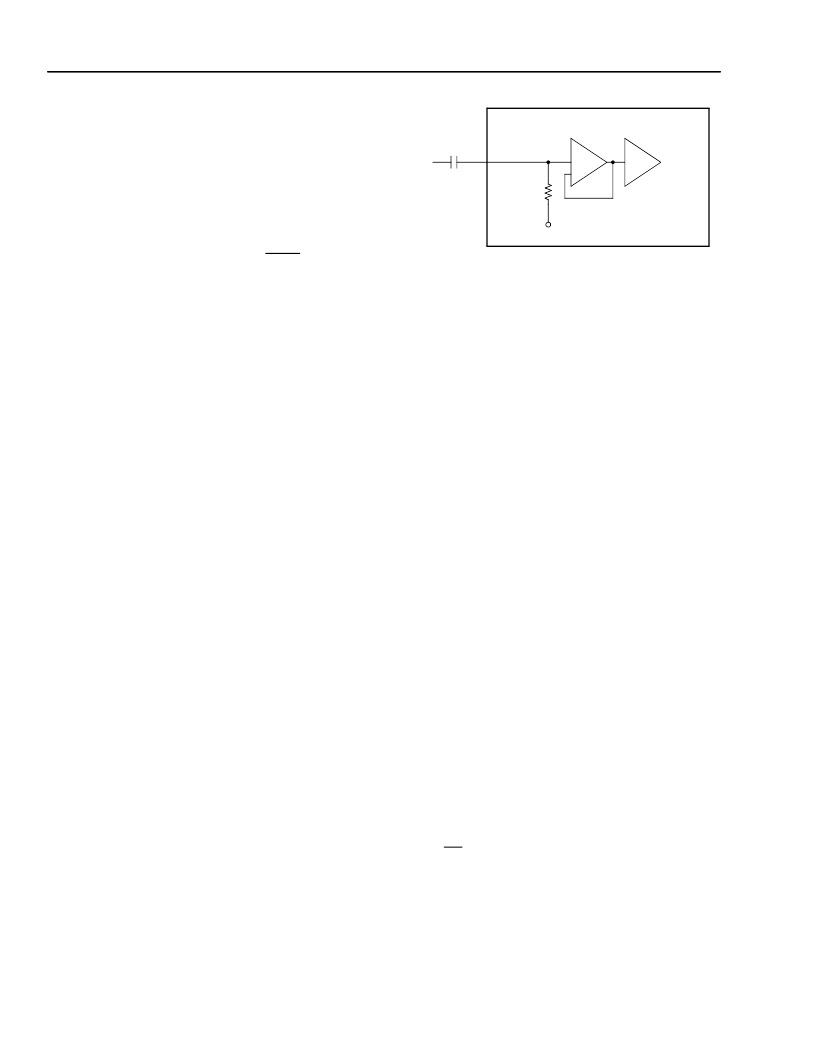

The analog input section (Figure 3) includes an on-chip

buffer op amp and internal gain. Feedback paths (Z

T

and HYBAL in Figure 1) are included in the T7507 to

generate signals needed for termination impedance

and hybrid balance.

When matched with a SLIC with a transconductance

from tip/ring of 39.75 V/A and a differential gain to

tip/ring of 2 (such as the Lucent Technologies L8567),

and when a solid-state switch (such as the Lucent

L7583) and 50

of series protection are used, the

T7507 will synthesize a complex line termination

impedance and hybrid balance network of 200

+

680

|| 100 nF. Additionally, the T7507 will fix the

line circuit tip/ring to PCM transmit gain at 0 dB (at

1000 Hz, –0.7 dB, +0.3 dB) and will allow a user-select-

able (via the serial control input) PCM to tip/ring receive

gain of –3.5 dB or –7.0 dB (at 1000 Hz, –0.7 dB,

+0.3 dB). Thus, the ac interface between the T7507

and the L8567 SLIC consists of a single dc blocking

capacitor in the transmit direction, and a direct connec-

tion requiring no external components in the receive

direction. The T7507/L8567/L7583 chip set is designed

to meet all MPT requirements for the People’s Republic

of China.

Transmission Levels

Zero transmission-level points are specified relative to

the digital milliwatt sequence prescribed by ITU-T rec-

ommendation G.711. Under these conditions, an ana-

log input of 0.0452 Vrms applied to VF

X

IN produces a

0 dBm digital code, while a 0 dBm code input at D

R

produces an output of 0.394 Vrms differentially at

VF

R

ON/VF

R

OP when using the –7.0 dB gain mode

(data bit D4 = 0).

5-4821(F)

Figure 3. Typical Analog Input Section

Microprocessor Serial Data Control and

L8567 SLIC/L7583 Switch (or EMR) Control

Interfaces

The basic logic control scheme is a serial data interface

between the microcontroller and the T7507. Through

this interface, an 8-bit input control word and an 8-bit

output status word is passed between the T7507 and

microcontroller. The input control word contains infor-

mation for the T7507, L8567 SLIC, and L7583 switch.

The output status word contains off-hook and thermal

shutdown status information from the L8567 SLIC and

L7583 switch. See the Input Word Definition and Out-

put Word Definition sections of this data sheet for spe-

cific details on the input and output words.

Control and status information are passed between the

T7507 and L8567 SLIC/L7583 switch via a latched par-

allel data interface. Data latches are integrated into the

L8567 SLIC inputs and outputs and L7583 switch

inputs. Thus, a given data I/O on the T7507 serves the

corresponding data I/O on the L8567 SLIC for the four

channels associated with the quad T7507. Additionally,

a given data output on the T7507 serves the corre-

sponding data inputs on the L7583 switch for the four

channels associated with the quad T7507. Status infor-

mation from the L7583 switch is passed to the T7507

on a per-line basis.

The T7507 control interface consists of an 8-bit input

serial shift register, an 8-bit output serial shift register,

an 8-bit loop status input latch, logic to generate the

enable (EN) pulses required to control the SLIC and

switch data latches, interface logic/buffers between the

DI shift register and the internal codec control, and

interface logic buffers between the SLIC/switch output

control leads.

SLIC

26 dB

TO

CODEC

FILTERS

T7507

C

1

≥

0.07

μ

F

VF

X

IN

R

≥

100 k

V

CM

= 2.4 V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7570 | T7570 Programmable PCM Codec with Hybrid-Balance Filter |

| T7630 | T7630 Dual T1/E1 5.0 V Short-Haul Terminator (Terminator-II) |

| T7630 | Dual T1/E1 5.0 V Short-Haul Terminator (Terminator-II)(雙 T1/E1 5.0V短距離通信終端器) |

| T8100A | H.100/H.110 Interface and Time-Slot Interchangers |

| T8102A | H.100/H.110 Interface and Time-Slot Interchangers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T75-08M2 | 制造商:The Cherry Corporation 功能描述: |

| T-751 | 制造商:RHOMBUS-IND 制造商全稱:Rhombus Industries Inc. 功能描述:Fly Back Transformer |

| T75-24C3 | 制造商:Stancor 功能描述:Power Transformer Triple Prim. Single Sec. 120V/208V/240V Prim. 24V Sec. Flange Mount |

| T7570 | 制造商:AGERE 制造商全稱:AGERE 功能描述:T7570 Programmable PCM Codec with Hybrid-Balance Filter |

| T-758 | 制造商:RHOMBUS-IND 制造商全稱:Rhombus Industries Inc. 功能描述:Transformer |

發(fā)布緊急采購,3分鐘左右您將得到回復。