- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300083 > V59C1G01408QAJ37E (PROMOS TECHNOLOGIES INC) 256M X 4 DDR DRAM, 0.5 ns, PBGA68 PDF資料下載

參數(shù)資料

| 型號(hào): | V59C1G01408QAJ37E |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | 256M X 4 DDR DRAM, 0.5 ns, PBGA68 |

| 封裝: | ROHS COMPLIANT, FBGA-68 |

| 文件頁數(shù): | 71/79頁 |

| 文件大小: | 1029K |

| 代理商: | V59C1G01408QAJ37E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁當(dāng)前第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁

73

ProMOS TECHNOLOGIES

V59C1G01(408/808/168)QA

V59C1G01(408/808/168)QA Rev. 1.2 April 2008

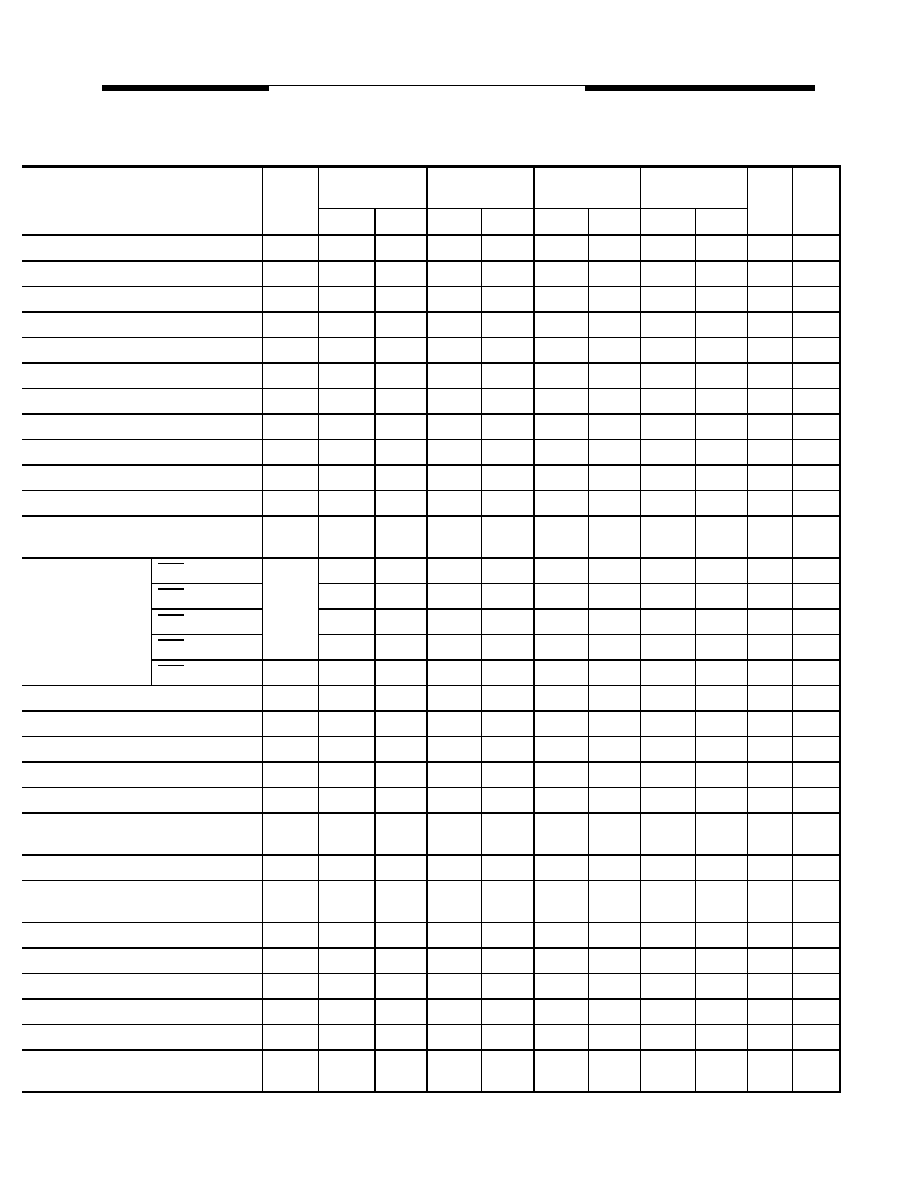

AC Characteristics (AC operating conditions unless otherwise noted)

Parameter

Symbol

(DDR2-667)

-3

(DDR2-800)

-25A

(DDR2-800)

-25

(DDR2-1066)

-18

Unit

Note

Min

Max

Min

Max

Min

Max

Min

Max

Row Cycle Time

tRC

54

-

54

-

57.5

-

58.125

-

ns

Auto Refresh Row Cycle Time

tRFC

105

-

105

-

105

-

105

-

ns

11

Row Active Time

tRAS

45

70K

45

70K

45

70K

45

70K

ns

21

Row Address to Column Address Delay

tRCD

15

-

15

-

12.5

-

13.125

-

ns

20

Row Active to Row Active Delay (x4 & x8)

tRRD

7.5

-

7.5

-

7.5

-

7.5

-

ns

Row Active to Row Active Delay (x16)

tRRD

10

-

10

-

10

-

10

-

ns

Four Activate Window for (x4 & x8)

tFAW

37.5

-

35

-

35

-

35

-

ns

Four Active to Row Active Delay (x16)

tFAW

50

-

45

-

45

-

45

-

ns

Column Address to Column Address Delay

tCCD

2

-

2

-

2

-

2

-

CLK

Row Precharge Time

tRP

15

-

15

-

12.5

-

13.125

-

ns

Write Recovery Time

tWR

15

-

15

-

15

-

15

-

ns

Auto Precharge Write Recovery + Precharge

Time

tDAL

tWR +tRP

-

tWR +tRP

-

tWR +tRP

-

tWR +tRP

-

ns

12

System Clock Cycle

Time

CAS Latency = 3

tCK

5

8

5

858

58

ns

2

CAS Latency = 4

3.75

8

3.75

8

3.75

8

3.75

8

ns

2

CAS Latency = 5

3

8

3

8

2.5

8

3

8

ns

2

CAS Latency = 6

3

82.582.582.5

8

ns

2

CAS Latency = 7

3

82.582.582.5

8

ns

2

Clock High Level Width

tCH

0.48

0.52

0.48

0.52

0.48

0.52

0.48

0.52

CLK

Clock Low Level Width

tCL

0.48

0.52

0.48

0.52

0.48

0.52

0.48

0.52

CLK

Data-Out edge to Clock edge Skew

tAC

-0.45

0.45

-0.40

0.40

-0.40

0.40

-0.35

0.35

ns

DQS-Out edge to Clock edge Skew

tDQSCK

-0.40

0.40

-0.35

0.35

-0.35

0.35

-0.325

0.325

ns

DQS-Out edge to Data-Out edge Skew

tDQSQ

-

0.24

-

0.20

-

0.20

-

0.175

ns

Data-Out hold time from DQS

tQH

tHPmin

-tQHS

-

tHPmin

-tQHS

-

tHPmin

-tQHS

-

tHPmin

-tQHS

-

ns

Data hold skew factor

tQHS

-

340

-

300

-

300

-

250

ps

Clock Half Period

tHP

tCH/L

min

-

tCH/L

min

-

tCH/L

min

-

tCH/L

min

-

ns

5

Input Setup Time (fast slew rate)

tIS

200

-

175

-

175

-

125

-

ps

15,17

Input Hold Time (fast slew rate)

tIH

275

-

250

-

250

-

200

-

ps

15,17

Input Pulse Width

tIPW

0.60

-

0.60

-

0.60

-

0.60

-

CLK

Write DQS High Level Width

tDQSH

0.35

CLK

Write DQS Low Level Width

tDQSL

0.35

CLK

CLK to First Rising edge of DQS-In

tDQSS

-0.25

tCK

+0.25

tCK

-0.25

tCK

+0.25

tCK

-0.25

tCK

+0.25

tCK

-0.25

tCK

+0.25

tCK

CLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V59C1G01408QAJ37I | 256M X 4 DDR DRAM, 0.5 ns, PBGA68 |

| V5D010EB4D | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.5A, 125VDC, 4.4mm, PANEL MOUNT |

| V5F110CB | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, PANEL MOUNT |

| V5PNF | CABLE TERMINATED, FEMALE, N CONNECTOR, THREAD-IN STUB SELF-FLARE |

| V5T110TB3 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.6A, 125VDC, 2.4mm, PANEL MOUNT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4E | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。