- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359412 > VPC3200A (MICRONAS SEMICONDUCTOR HOLDING AG) Comb Filter Video Processor PDF資料下載

參數(shù)資料

| 型號(hào): | VPC3200A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類(lèi): | 消費(fèi)家電 |

| 英文描述: | Comb Filter Video Processor |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | PLASTIC, QFP-80 |

| 文件頁(yè)數(shù): | 24/78頁(yè) |

| 文件大小: | 1245K |

| 代理商: | VPC3200A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)

VPC 323xD, VPC 324xD

ADVANCE INFORMATION

24

Micronas

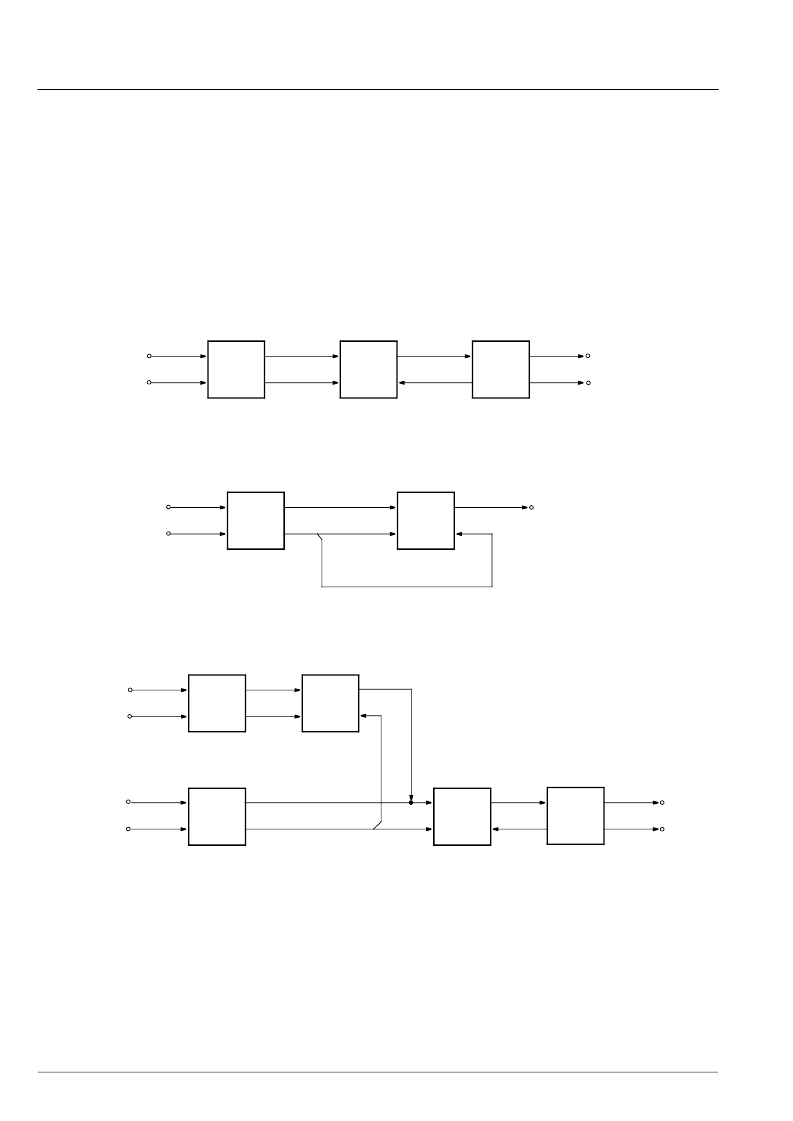

2.12. Picture in Picture (PIP) Processing and

Control

2.12.1. Configurations

To support PIP and/or scan rate conversion (SRC)

applications, the VPC32xxD provides several control

signals for an external field memory IC.

Fig. 2–21 demonstrates two applications with a single

VPC 32xxD. In these cases the VPC

single

writes the

main picture or one of several inset picture(s) into the

field memory. Only one of these pictures is displayed

live. These configurations are suitable for features

such as turner scan, still picture, still in picture and

simple scan rate conversion.

Fig. 2–22 shows an enhanced configuration with two

VPC 32xxD’s. In this case, one live and several still

pictures are inserted into the main live video signal.

The VPC

pip

processes the inset picture and writes the

original or decimated picture into the field memory.

The VPC

main

delivers the main picture, combines it

with the inset picture(s) from the field memory and

stores the combined video signal into a second field

memory for the SRC.

Fig. 2–21:

Typical configurations with single VPC 32xxD

Fig. 2–22:

Enhanced configuration with two VPC 32xxD

VPC

32XXD

(single)

field

memory

DDP

3310B

YC

r

C

b

/RGB

CVBS

YC

r

C

b

LLC1,

RSTWR,

WE, IE

YC

r

C

b

RGB

H/V

Def.

LLC2,

FIFORRD,

FIFORD

VPC

32XXD

(single)

YC

r

C

b

/RGB

CVBS

YC

r

C

b

LLC1,

RSTWR,

WE, IE

YC

r

C

b

field

memory

LLC1,

RSTWR,

RE

VPC

32XXD

(pip)

VPC

32XXD

(main)

field

memory

(for PIP)

field

memory

(for SRC)

DDP

3310B

YC

r

C

b

/RGB

CVBS

YC

r

C

b

/RGB

CVBS

(for main picture)

(for PIP)

YC

r

C

b

LLC1,

RSTWR,

WE, IE

YC

r

C

b

YC

r

C

b

LLC1,

RSTWR,

RE, OE

LLC1,

RSTWR,

WE, IE

RGB

H/V

Def.

LLC2,

FIFORRD,

FIFORD

YC

r

C

b

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPDV1CHP | TRANSISTOR | MOSFET | P-CHANNEL | 100V V(BR)DSS | CHIP |

| VPDV2CHP | TRANSISTOR | MOSFET | P-CHANNEL | 240V V(BR)DSS | CHIP |

| VPE28W12D | Analog IC |

| VPE28W15D | Analog IC |

| VPF2805D | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPC3200APSGP | 制造商:MICRONAS 功能描述:New |

| VPC3201A | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3205C | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3210A | 制造商:MICRONAS 制造商全稱(chēng):MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3210B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Consumer IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。