- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359412 > VPC3200A (MICRONAS SEMICONDUCTOR HOLDING AG) Comb Filter Video Processor PDF資料下載

參數(shù)資料

| 型號: | VPC3200A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Comb Filter Video Processor |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | PLASTIC, QFP-80 |

| 文件頁數(shù): | 41/78頁 |

| 文件大小: | 1245K |

| 代理商: | VPC3200A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁

ADVANCE INFORMATION

VPC 323xD, VPC 324xD

Micronas

41

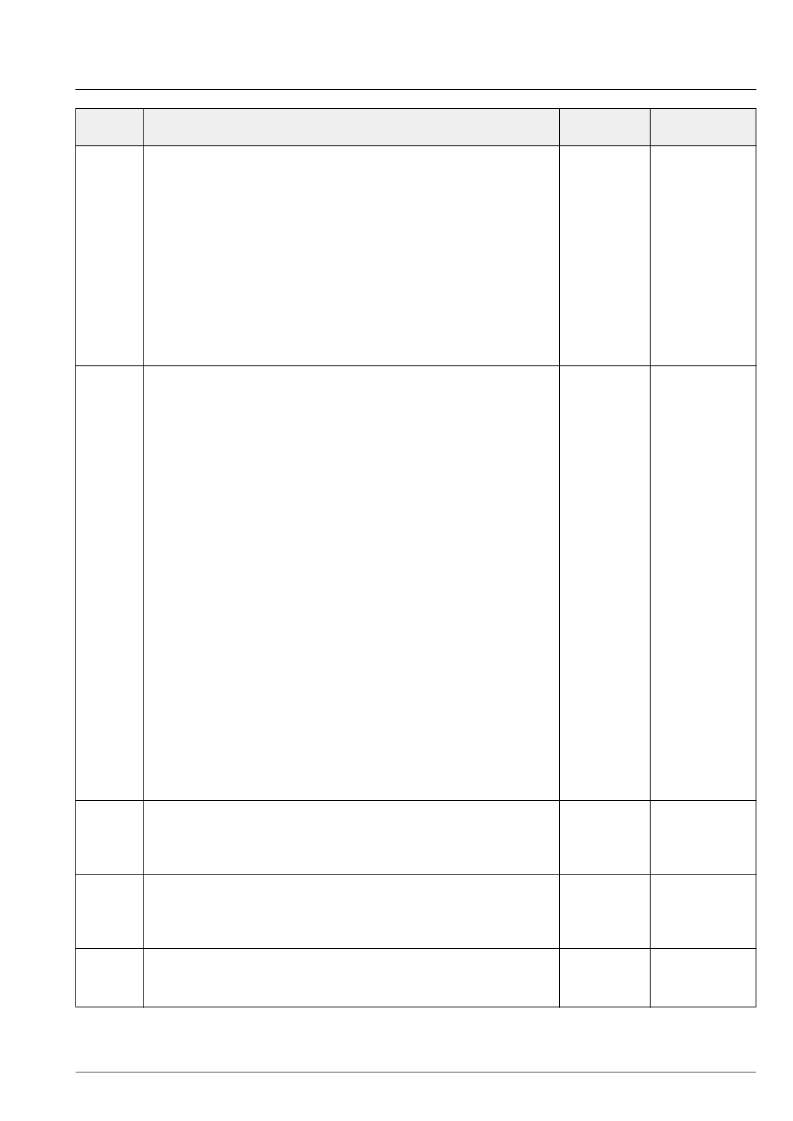

h’14e

Status of automatic standard recognition

bit[0]

1

error of the vertical standard (neither 50 nor 60 Hz)

bit[1]

1

detected standard is disabled

bit[2]

1

search active

bit[3]

1

search terminated, but failed

bit[3:0]

0000 all ok

0001 search not started, because vwin error detected

(no input or SECAM L)

0010 search not started, because detected vert. standard

not enabled

x1x0 search started and still active

1x00 search failed (found standard not correct)

1x10 search failed, (detected color standard not enabled)

0

ASR_STATUS

VWINERR

DISABLED

BUSY

FAILED

h’21

Input select:

writing to this register will also initialize the standard

bit[1:0]

luma selector

VIN3

VIN2

VIN1

VIN4

chroma selector

VIN1/CIN

IF compensation

off

6 dB/Okt

12 dB/Okt

10 dB/MHz only for SECAM

chroma bandwidth selector

narrow

normal

broad

wide

adaptive/fixed SECAM notch filter

enable luma lowpass filter

hpll speed

no change

terrestrial

vcr

mixed

status bit, write 0, this bit is set to 1 to indicate

operation complete.

00

01

10

11

bit[2]

0/1

bit[4:3]

00

01

10

11

bit[6:5]

00

01

10

11

0/1

0/1

bit[7]

bit[8]

bit[10:9]

00

01

10

11

bit[11]

0

1

0

2

0

0

3

INSEL

VIS

CIS

IFC

CBW

FNTCH

LOWP

HPLLMD

h’22

picture start position: This register sets the start point of active video

and can be used e.g. for panning. The setting is updated when ‘sdt’

register is updated or when the scaler mode register ‘scmode’ is writ-

ten.

0

SFIF

h’23

luma/chroma delay adjust. The setting is updated when ‘sdt’ register

is updated.

bit[5:0]

reserved, set to zero

bit[11:6]

luma delay in clocks, allowed range is +1 ... –7

0

LDLY

h’29

helper delay register (PAL+ mode only)

bit[11:0]

delay adjust for helper lines adjustable from

–96...96, 1 step corresponds to 1/32 clock

0

HLP_DLY

FP Sub-

address

Function

Default

Name

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPDV1CHP | TRANSISTOR | MOSFET | P-CHANNEL | 100V V(BR)DSS | CHIP |

| VPDV2CHP | TRANSISTOR | MOSFET | P-CHANNEL | 240V V(BR)DSS | CHIP |

| VPE28W12D | Analog IC |

| VPE28W15D | Analog IC |

| VPF2805D | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPC3200APSGP | 制造商:MICRONAS 功能描述:New |

| VPC3201A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3205C | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3210A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3210B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。