- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359412 > VPC3200A (MICRONAS SEMICONDUCTOR HOLDING AG) Comb Filter Video Processor PDF資料下載

參數(shù)資料

| 型號(hào): | VPC3200A |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | Comb Filter Video Processor |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封裝: | PLASTIC, QFP-80 |

| 文件頁(yè)數(shù): | 29/78頁(yè) |

| 文件大?。?/td> | 1245K |

| 代理商: | VPC3200A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)

ADVANCE INFORMATION

VPC 323xD, VPC 324xD

Micronas

29

2.12.9. External Field Memory

The requirements of the external field memory are:

– FIFO type access with reset

– write mask function: The increasing of the write

address pointer and the over writing of the data

should be controlled separately.

– output disable function: tri-statetable outputs

For PIP applications, VPC 32xxD supports 4:1:1 or

4:2:2 chrominance format. Table 2–13 shows the typi-

cal memory size for a 13.5 and 16 MHz system clock

application.

The following 5 signals are generated by VPC 32xxD

to control the external field memory:

RSTWR

(reset write/read) resets the internal write/

read address pointer to zero.

WE

(write enable) is used to enable or disable incre-

menting of the internal write address pointer.

IE

(input enable) is used to enable writing data from

the field memory input pins into the memory core, or to

disable writing and thereby preserving the previous

content of the memory (write mask function).

RE

(read enable) is used to enable or disable incre-

menting the internal read address pointer.

OE

(output enable) is used to enable or disable data

output to the output pins.

As serial write and serial read clock (

SWCK

and

SRCK

, respectively) of the field memory the line

locked clocks LLC1 and/or LLC2 are used.

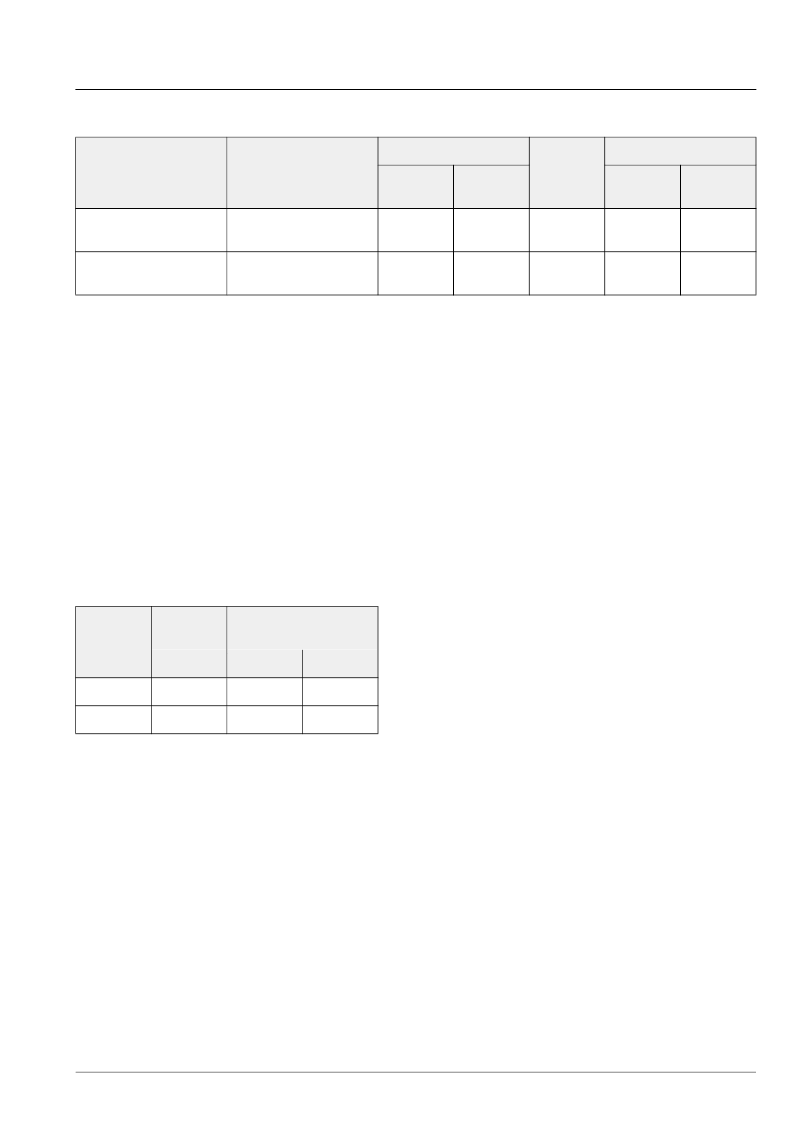

Table 2–12:

Settings for Free-Running Mode

Control bit

Function

VPC

single

VPC

pip

VPC

main

write

PIP

write main

pic.

predef.

mode 6, 10

all other

modes

bit[11] of LLC_CLKC

(FP h’6a)

enable/disable

LLC PLL

1

0

0

1

0

bit[15] of AVO START

(I

2

C h’28)

enable/disable free-

running sync mode

1

0

0

1

0

Table 2–13:

Word length and minimum size of the field

memory

Chromi-

nance

format

Word

length

Memory size

[bit]

[word]

[bit]

4:1:1

12

245376

2944512

4:2:2

16

245376

3926016

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPDV1CHP | TRANSISTOR | MOSFET | P-CHANNEL | 100V V(BR)DSS | CHIP |

| VPDV2CHP | TRANSISTOR | MOSFET | P-CHANNEL | 240V V(BR)DSS | CHIP |

| VPE28W12D | Analog IC |

| VPE28W15D | Analog IC |

| VPF2805D | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPC3200APSGP | 制造商:MICRONAS 功能描述:New |

| VPC3201A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3205C | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3210A | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Comb Filter Video Processor |

| VPC3210B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。