- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361836 > WEDPNF8M722V-XBX 8Mx72 Synchronous DRAM + 16Mb Flash Mixed Module(8Mx72同步動態(tài)RAM+16M位閃速存儲器混合型模塊) PDF資料下載

參數(shù)資料

| 型號: | WEDPNF8M722V-XBX |

| 英文描述: | 8Mx72 Synchronous DRAM + 16Mb Flash Mixed Module(8Mx72同步動態(tài)RAM+16M位閃速存儲器混合型模塊) |

| 中文描述: | 8Mx72同步DRAM 16Mb的閃存混合模塊(8Mx72同步動態(tài)RAM的1,600位閃速存儲器混合型模塊) |

| 文件頁數(shù): | 14/41頁 |

| 文件大?。?/td> | 522K |

| 代理商: | WEDPNF8M722V-XBX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁

14

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

WEDPNF8M722V-XBX

NOTES:

1. The minimum specifications are used only to indicate cycle time at which

proper operation over the full temperature range is ensured.

2. An initial pause of 100ms is required after power-up, followed by two

AUTO REFRESH commands, before proper device operation is ensured.

(V

CC

must be powered up simultaneously.) The two AUTO REFRESH

command wake-ups should be repeated any time the t

REF

refresh require-

ment is exceeded.

3. AC characteristics assume t

T

= 1ns.

4. In addition to meeting the transition rate specification, the clock and CKE

must transit between V

IH

and V

IL

(or between V

IL

and V

IH

) in a monotonic

manner.

5. Outputs measured at 1.5V with equivalent load:

6. AC timing and I

CC

tests have V

IL

= 0V and V

IH

= 3V, with timing referenced

to 1.5V crossover point.

7. Timing actually specified by t

CKS

; clock(s) specified as a reference only at

minimum cycle rate.

8. Timing actually specified by t

WR

plus t

RP

; clock(s) specified as a reference

only at minimum cycle rate.

9. Timing actually specified by t

WR

.

10. Required clocks are specified by JEDEC functionality and are not depen-

dent on any timing parameter.

11. JEDEC and PC100 specify three clocks.

Q

50pF

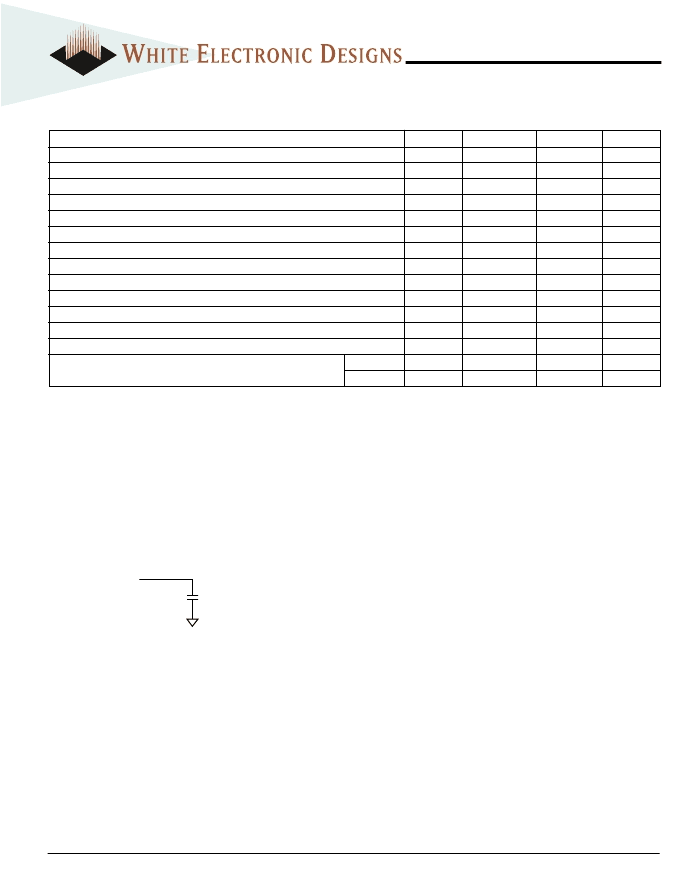

SDRAM AC FUNCTIONAL CHARACTERISTICS

(Notes 1,2,3,4,5,6)

Parameter/Condition

READ/WRITE command to READ/WRITE command (10)

CKE to clock disable or power-down entry mode (7)

CKE to clock enable or power-down exit setup mode (7)

DQM to input data delay (10)

DQM to data mask during WRITEs

DQM to data high-impedance during READs

WRITE command to input data delay (10)

Data-in to ACTIVE command (8)

Data-in to PRECHARGE command (9)

Last data-in to burst STOP command (10)

Last data-in to new READ/WRITE command (10)

Last data-in to PRECHARGE command (9)

LOAD MODE REGISTER command to ACTIVE or REFRESH command (11)

Symbol

t

CCD

t

CKED

t

PED

t

DQD

t

DQM

t

DQZ

t

DWD

t

DAL

t

DPL

t

BDL

t

CDL

t

RDL

t

MRD

t

ROH

t

ROH

-100

1

1

1

0

0

2

0

4

2

1

1

2

2

3

2

-125

1

1

1

0

0

2

0

5

2

1

1

2

2

3

—

Units

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

t

CK

Data-out to high-impedance from PRECHARGE command (10)

CL = 3

CL = 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| WEDPS512K32V-XBX | SRAM MCP |

| WEDPS512K32-XBX | SRAM MCP |

| WEDPY256K72V-XBX | SSRAM MCP |

| WEDPZ512K72S-XBX | NBL SSRAM MCP |

| WEDPZ512K72V-XBX | NBL SSRAM MCP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WEDPS512K32-12BC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:512Kx32 SRAM MULTI-CHIP PACKAGE |

| WEDPS512K32-12BI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:512Kx32 SRAM MULTI-CHIP PACKAGE |

| WEDPS512K32-12BM | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:512Kx32 SRAM MULTI-CHIP PACKAGE |

| WEDPS512K32-15BC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:512Kx32 SRAM MULTI-CHIP PACKAGE |

| WEDPS512K32-15BI | 制造商:White Electronic Designs 功能描述:SRAM Module Asynchronous 16Mbit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。