- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1974 > XE8807AMI026TLF (Semtech)IC MCU LOW PWR MTP FLASH 32-TQFP PDF資料下載

參數(shù)資料

| 型號: | XE8807AMI026TLF |

| 廠商: | Semtech |

| 文件頁數(shù): | 94/143頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC MCU LOW PWR MTP FLASH 32-TQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | XE880x |

| 應(yīng)用: | 感測機(jī) |

| 核心處理器: | Coolrisc816? |

| 程序存儲器類型: | 閃存(11 kB) |

| 控制器系列: | XE8000 |

| RAM 容量: | 512 x 8 |

| 接口: | UART,USRT |

| 輸入/輸出數(shù): | 24 |

| 電源電壓: | 2.4 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 32-TQFP |

| 包裝: | 標(biāo)準(zhǔn)包裝 |

| 供應(yīng)商設(shè)備封裝: | 32-TQFP(7x7) |

| 產(chǎn)品目錄頁面: | 585 (CN2011-ZH PDF) |

| 配用: | XE8000MP-ND - PROG BOARD AND PROSTART2 CARD |

| 其它名稱: | XE8807AMI026DKR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁當(dāng)前第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁

Semtech 2006

www.semtech.com

8-4

XE8806A/XE8807A

pos.

RegIrqEnMid

rw

reset

function

7

RegIrqEnMid[7]

rw

0

1= enable interrupt #15

6

RegIrqEnMid[6]

rw

0

1= enable interrupt #14

5

RegIrqEnMid[5]

rw

0

1= enable interrupt #13

4

RegIrqEnMid[4]

rw

0

1= enable interrupt #12

3

RegIrqEnMid[3]

rw

0

1= enable interrupt #11

2

RegIrqEnMid[2]

rw

0

1= enable interrupt #10

1

RegIrqEnMid[1]

rw

0

1= enable interrupt #9

0

RegIrqEnMid[0]

rw

0

1= enable interrupt #8

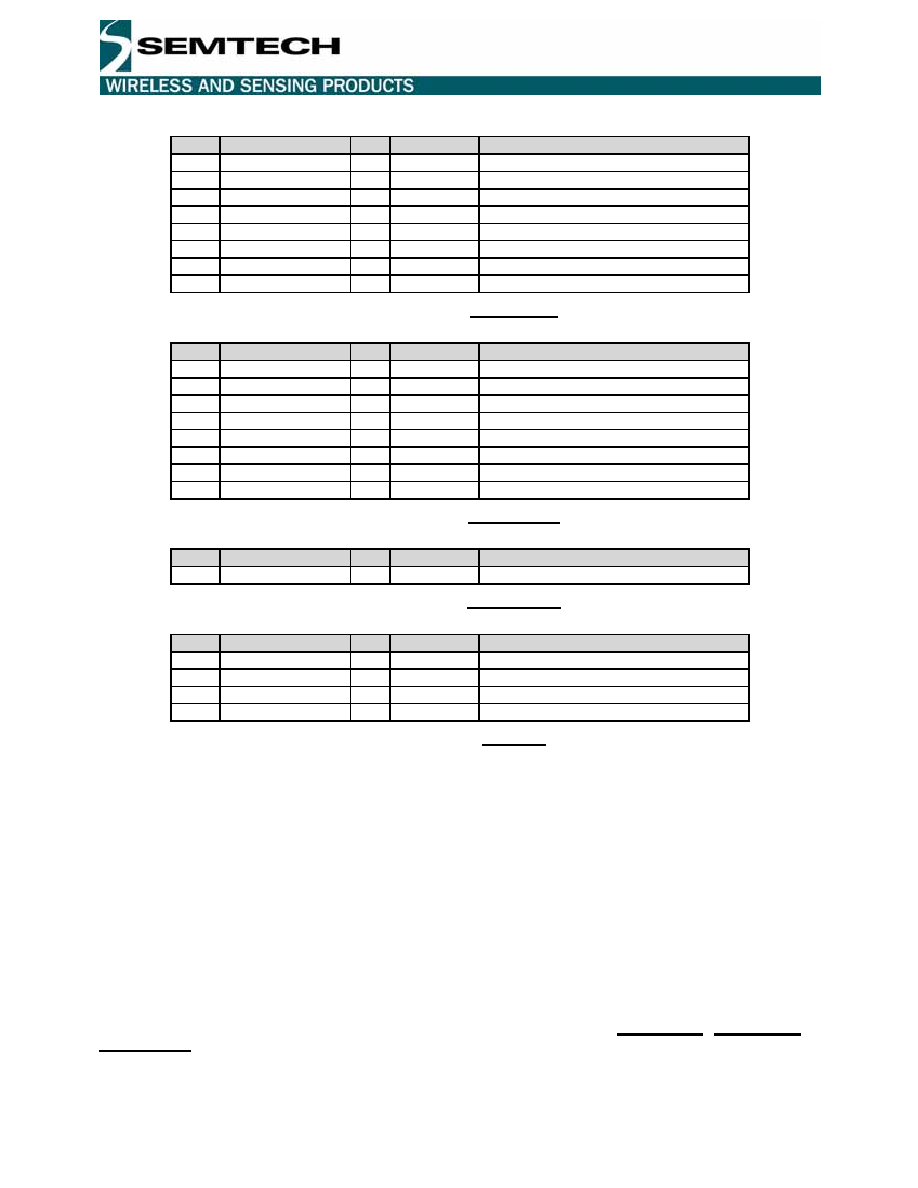

Table 8-6: RegIrqEnMid

pos.

RegIrqEnLow

rw

reset

function

7

RegIrqEnLow[7]

rw

0

1= enable interrupt #7

6

RegIrqEnLow[6]

rw

0

1= enable interrupt #6

5

RegIrqEnLow[5]

rw

0

1= enable interrupt #5

4

RegIrqEnLow[4]

rw

0

1= enable interrupt #4

3

RegIrqEnLow[3]

rw

0

1= enable interrupt #3

2

RegIrqEnLow[2]

rw

0

1= enable interrupt #2

1

RegIrqEnLow[1]

rw

0

1= enable interrupt #1

0

RegIrqEnLow[0]

rw

0

1= enable interrupt #0

Table 8-7: RegIrqEnLow

pos.

RegIrqPriority

rw

reset

function

7-0

RegIrqPriority

r

11111111

code of highest priority set

Table 8-8: RegIrqPriority

pos.

RegIrqIrq

rw

reset

function

7-3

-

r

00000

unused

2

IrqHig

r

0

one or more high priority interrupts is set

1

IrqMid

r

0

one or more mid priority interrupts is set

0

IrqLow

r

0

one or more low priority interrupts is set

Table 8-9: RegIrqIrq

8.4

Detailed description

The CoolRISC core has 3 different interrupt levels IN0, IN1 and IN2 (Figure 8-1). When these interrupts are

triggered, the program counter (PC) is loaded with a fixed address. In case more than one interrupt occurs

simultaneously, the execution order is IN0, IN1, IN2.

The masking, setting and clearing of these interrupts can be done in the stat register (see chapter describing the

CPU).

The interrupt handler bundles a certain number of interrupt sources and routes them to one of these three

interrupts and provides the possibility to enable/disable each of them individually. The definition of the interrupt

sources is given in the memory mapping chapter.

RegIrqHig, RegIrqMid, and RegIrqLow are 8-bit registers containing flags for the interrupt sources. Those flags are

set when the interrupt is enabled (i.e. if the corresponding bit in the registers RegIrqEnHig, RegIrqEnMid or

RegIrqEnLow is set) and a rising edge is detected on the corresponding interrupt source.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XIO2200AGGW | IC PCI-EXPRESS/BUS BRIDGE 176BGA |

| XIO2200AZGW | IC PCI-EXPRESS/BUS BRIDGE 176BGA |

| XPC823ZT81B2T | IC MPU POWERQUICC 81MHZ 256-PBGA |

| XPC8240RZU250E | MCU HOST PROCESSOR 352-TBGA |

| XQ6SLX150T-3CSG484I | IC FPGA SPARTAN-6Q 484-CSBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XE88LC01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Sensing Machine 16 + 10 bit Data Acquisition Ultra Low-Power Microcontroller |

| XE88LC01MI000 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Sensing Machine 16 + 10 bit Data Acquisition Ultra Low-Power Microcontroller |

| XE88LC01MI027 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Sensing Machine 16 + 10 bit Data Acquisition Ultra Low-Power Microcontroller |

| XE88LC01MI032 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Sensing Machine 16 + 10 bit Data Acquisition Ultra Low-Power Microcontroller |

| XE88LC01RI000 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Sensing Machine 16 + 10 bit Data Acquisition Ultra Low-Power Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。