- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19474 > ADSP-2105BPZ-80 (Analog Devices Inc)IC DSP CONTROLLER 16BIT 68PLCC PDF資料下載

參數(shù)資料

| 型號: | ADSP-2105BPZ-80 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 16/64頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DSP CONTROLLER 16BIT 68PLCC |

| 標準包裝: | 19 |

| 系列: | ADSP-21xx |

| 類型: | 定點 |

| 接口: | 同步串行端口(SSP) |

| 時鐘速率: | 20MHz |

| 非易失內(nèi)存: | 外部 |

| 芯片上RAM: | 3kB |

| 電壓 - 輸入/輸出: | 5.00V |

| 電壓 - 核心: | 5.00V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁面: | 738 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

ADSP-21xx

REV. B

–23–

POWER DISSIPATION EXAMPLE

To determine total power dissipation in a specific application,

the following equation should be applied for each output:

C

× V

DD

2

× f

C = load capacitance, f = output switching frequency.

Example:

In an ADSP-2111 application where external data memory is

used and no other outputs are active, power dissipation is

calculated as follows:

Assumptions:

External data memory is accessed every cycle with 50% of the

address pins switching.

External data memory writes occur every other cycle with

50% of the data pins switching.

Each address and data pin has a 10 pF total load at the pin.

The application operates at V

DD = 5.0 V and tCK = 50 ns.

Total Power Dissipation = PINT + (C × VDD

2

× f )

PINT = internal power dissipation (from Figure 17).

(C

× V

DD

2

× f ) is calculated for each output:

# of

Output

Pins

× C

× V

DD

2

× f

Address, DMS 8

× 10 pF × 52 V × 20 MHz = 40.0 mW

Data, WR

9

× 10 pF × 52 V × 10 MHz = 22.5 mW

RD

1

× 10 pF × 52 V × 10 MHz = 2.5 mW

CLKOUT

1

× 10 pF × 52 V × 20 MHz = 5.0 mW

70.0 mW

Total power dissipation for this example = PINT + 70.0 mW.

ENVIRONMENTAL CONDITIONS

Ambient Temperature Rating:

TAMB = TCASE – (PD

× θ

CA)

TCASE = Case Temperature in

°C

PD = Power Dissipation in W

θ

CA = Thermal Resistance (Case-to-Ambient)

θ

JA = Thermal Resistance (Junction-to-Ambient)

θ

JC = Thermal Resistance (Junction-to-Case)

Package

θ

JA

θ

JC

θ

CA

PGA

35

°C/W

18

°C/W

17

°C/W

PQFP

42

°C/W

18

°C/W

23

°C/W

SPECIFICATIONS (ADSP-2111)

CAPACITIVE LOADING

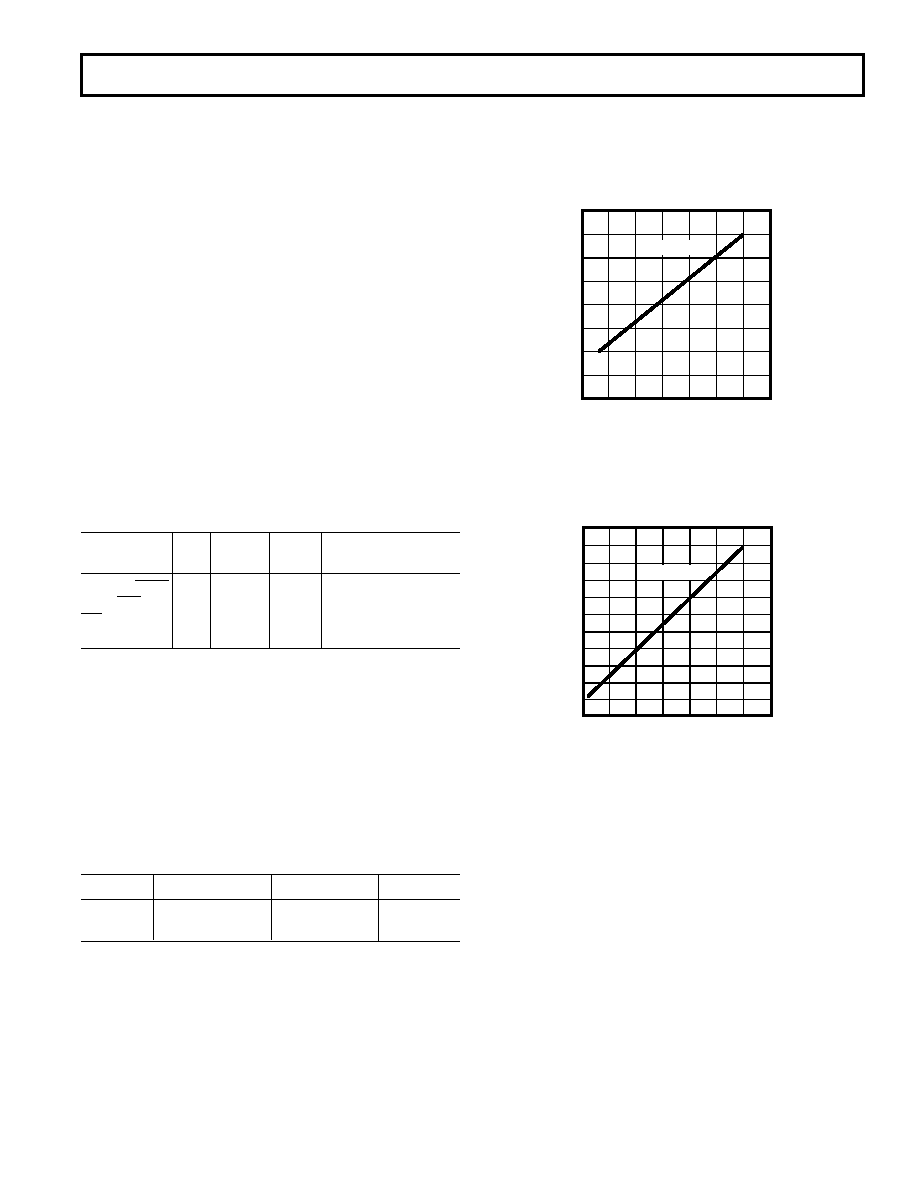

Figures 18 and 19 show capacitive loading characteristics for the

ADSP-2111.

CL – pF

25

150

125

100

75

50

RISE

TIME

(0.8V

-

2.0V)

–

ns

14

2

6

4

8

10

12

VDD = 4.5V

Figure 18. Typical Output Rise Time vs. Load Capacitance, C

L

(at Maximum Ambient Operating Temperature)

CL – pF

25

100

125

50

75

150

VALID

OUTPUT

DELAY

OR

HOLD

–

ns

+10

–2

–6

–4

+4

+2

+6

+8

+12

NOMINAL

VDD = 4.5V

Figure 19. Typical Output Valid Delay or Hold vs. Load

Capacitance, C

L (at Maximum Ambient Operating Temperature)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EEM06DTMH | CONN EDGECARD 12POS R/A .156 SLD |

| HSC40DRTF-S13 | CONN EDGECARD 80POS .100 EXTEND |

| XC95288XL-7FG256C | IC CPLD 288 MCELL C-TEMP 256FBGA |

| VI-B7L-CX-B1 | CONVERTER MOD DC/DC 28V 75W |

| TAP336J010CRW | CAP TANT 33UF 10V 5% RADIAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2105BPZ-80 | 制造商:Analog Devices 功能描述:IC 16-BIT MICROCOMPUTER |

| ADSP-2105BPZ-80RL | 制造商:Analog Devices 功能描述: |

| ADSP-2105KP-40 | 制造商:Analog Devices 功能描述:Digital Signal Processor, 16 Bit, 68 Pin, Plastic, PLCC |

| ADSP2105KP55 | 制造商:AD 功能描述:* |

| ADSP-2105KP-55 | 制造商:Analog Devices 功能描述:SEMICONDUCTOR ((NW)) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。