- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19474 > ADSP-2105BPZ-80 (Analog Devices Inc)IC DSP CONTROLLER 16BIT 68PLCC PDF資料下載

參數(shù)資料

| 型號: | ADSP-2105BPZ-80 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 46/64頁 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 16BIT 68PLCC |

| 標(biāo)準(zhǔn)包裝: | 19 |

| 系列: | ADSP-21xx |

| 類型: | 定點(diǎn) |

| 接口: | 同步串行端口(SSP) |

| 時(shí)鐘速率: | 20MHz |

| 非易失內(nèi)存: | 外部 |

| 芯片上RAM: | 3kB |

| 電壓 - 輸入/輸出: | 5.00V |

| 電壓 - 核心: | 5.00V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁面: | 738 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

ADSP-21xx

–50–

REV. B

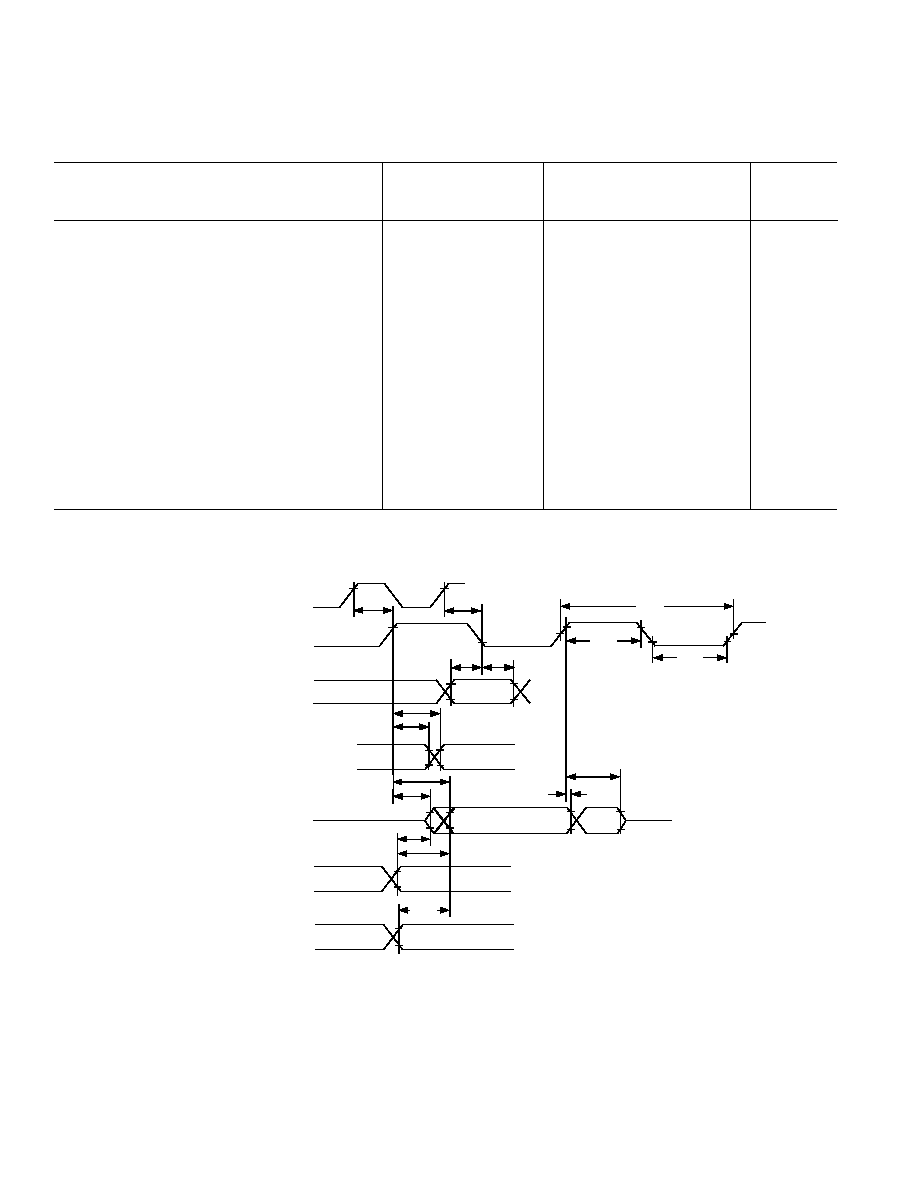

TIMING PARAMETERS (ADSP-2103/2162/2164)

SERIAL PORTS

Frequency

10.24 MHz

Dependency

Parameter

Min

Max

Min

Max

Unit

Timing Requirement:

tSCK

SCLK Period

97.6

tCK

ns

tSCS

DR/TFS/RFS Setup before SCLK Low

8

ns

tSCH

DR/TFS/RFS Hold after SCLK Low

10

ns

tSCP

SCLKin Width

28

ns

Switching Characteristic:

tCC

CLKOUT High to SCLKout

24.4

39.4

0.25tCK

ns

tSCDE

SCLK High to DT Enable

0

ns

tSCDV

SCLK High to DT Valid

28

ns

tRH

TFS/RFSout Hold after SCLK High

0

ns

tRD

TFS/RFSout Delay from SCLK High

28

ns

tSCDH

DT Hold after SCLK High

0

ns

tTDE

TFS (alt) to DT Enable

0

ns

tTDV

TFS (alt) to DT Valid

18

ns

tSCDD

SCLK High to DT Disable

30

ns

tRDV

RFS (Multichannel, Frame Delay Zero)

20

ns

to DT Valid

CLKOUT

SCLK

TFS

RFS

DR

RFSIN

TFSIN

DT

( ALTERNATE

FRAME MODE )

t

CC

t

CC

t

SCK

t

SCP

t

SCP

t

SCS

t

SCH

t

RD

t

RH

RFSOUT

TFSOUT

t

SCDV

t

SCDE

t

SCDH

t

SCDD

t

TDE

t

TDV

t

RDV

( MULTICHANNEL MODE,

FRAME DELAY 0 {MFD = 0} )

Figure 44. Serial Ports

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EEM06DTMH | CONN EDGECARD 12POS R/A .156 SLD |

| HSC40DRTF-S13 | CONN EDGECARD 80POS .100 EXTEND |

| XC95288XL-7FG256C | IC CPLD 288 MCELL C-TEMP 256FBGA |

| VI-B7L-CX-B1 | CONVERTER MOD DC/DC 28V 75W |

| TAP336J010CRW | CAP TANT 33UF 10V 5% RADIAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2105BPZ-80 | 制造商:Analog Devices 功能描述:IC 16-BIT MICROCOMPUTER |

| ADSP-2105BPZ-80RL | 制造商:Analog Devices 功能描述: |

| ADSP-2105KP-40 | 制造商:Analog Devices 功能描述:Digital Signal Processor, 16 Bit, 68 Pin, Plastic, PLCC |

| ADSP2105KP55 | 制造商:AD 功能描述:* |

| ADSP-2105KP-55 | 制造商:Analog Devices 功能描述:SEMICONDUCTOR ((NW)) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。