- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19474 > ADSP-2105BPZ-80 (Analog Devices Inc)IC DSP CONTROLLER 16BIT 68PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-2105BPZ-80 |

| 廠商: | Analog Devices Inc |

| 文件頁(yè)數(shù): | 22/64頁(yè) |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 16BIT 68PLCC |

| 標(biāo)準(zhǔn)包裝: | 19 |

| 系列: | ADSP-21xx |

| 類型: | 定點(diǎn) |

| 接口: | 同步串行端口(SSP) |

| 時(shí)鐘速率: | 20MHz |

| 非易失內(nèi)存: | 外部 |

| 芯片上RAM: | 3kB |

| 電壓 - 輸入/輸出: | 5.00V |

| 電壓 - 核心: | 5.00V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁(yè)面: | 738 (CN2011-ZH PDF) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

ADSP-21xx

REV. B

–29–

GENERAL NOTES

Use the exact timing information given. Do not attempt to

derive parameters from the addition or subtraction of others.

While addition or subtraction would yield meaningful results for

an individual device, the values given in this data sheet reflect

statistical variations and worst cases. Consequently, you cannot

meaningfully add parameters to derive longer times.

TIMING NOTES

Switching characteristics specify how the processor changes its

signals. You have no control over this timing—circuitry external

to the processor must be designed for compatibility with these

signal characteristics. Switching characteristics tell you what the

processor will do in a given circumstance. You can also use

TIMING PARAMETERS (ADSP-2101/2105/2111/2115/2161/2163)

switching characteristics to ensure that any timing requirement

of a device connected to the processor (such as memory) is

satisfied.

Timing requirements apply to signals that are controlled by

circuitry external to the processor, such as the data input for a

read operation. Timing requirements guarantee that the

processor operates correctly with other devices.

MEMORY REQUIREMENTS

The table below shows common memory device specifications

and the corresponding ADSP-21xx timing parameters, for your

convenience.

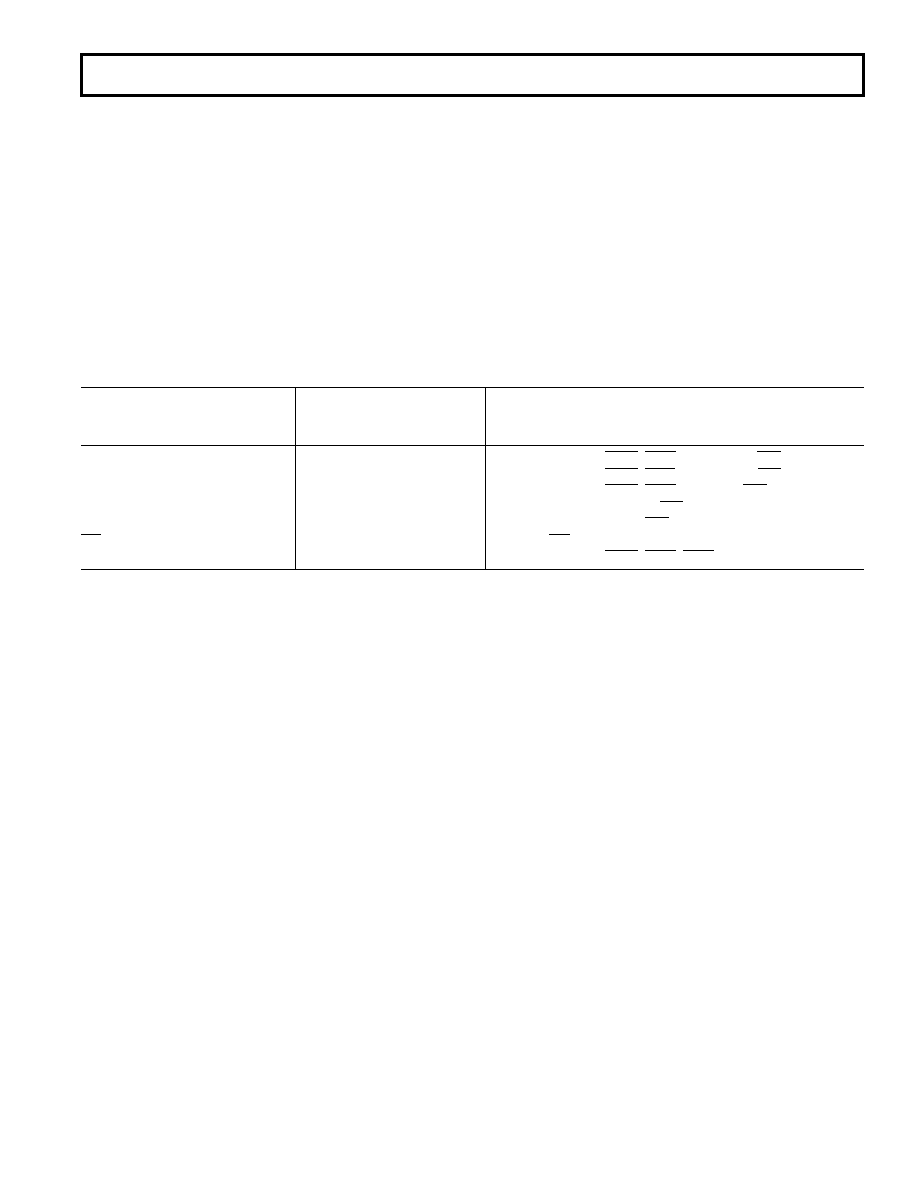

Memory

ADSP-21xx

Timing

Device

Timing

Parameter

Specification

Parameter

Definition

Address Setup to Write Start

tASW

A0–A13, DMS, PMS Setup before WR Low

Address Setup to Write End

tAW

A0–A13, DMS, PMS Setup before WR Deasserted

Address Hold Time

tWRA

A0–A13, DMS, PMS Hold after WR Deasserted

Data Setup Time

tDW

Data Setup before WR High

Data Hold Time

tDH

Data Hold after WR High

OE to Data Valid

tRDD

RD Low to Data Valid

Address Access Time

tAA

A0–A13, DMS, PMS, BMS to Data Valid

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EEM06DTMH | CONN EDGECARD 12POS R/A .156 SLD |

| HSC40DRTF-S13 | CONN EDGECARD 80POS .100 EXTEND |

| XC95288XL-7FG256C | IC CPLD 288 MCELL C-TEMP 256FBGA |

| VI-B7L-CX-B1 | CONVERTER MOD DC/DC 28V 75W |

| TAP336J010CRW | CAP TANT 33UF 10V 5% RADIAL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2105BPZ-80 | 制造商:Analog Devices 功能描述:IC 16-BIT MICROCOMPUTER |

| ADSP-2105BPZ-80RL | 制造商:Analog Devices 功能描述: |

| ADSP-2105KP-40 | 制造商:Analog Devices 功能描述:Digital Signal Processor, 16 Bit, 68 Pin, Plastic, PLCC |

| ADSP2105KP55 | 制造商:AD 功能描述:* |

| ADSP-2105KP-55 | 制造商:Analog Devices 功能描述:SEMICONDUCTOR ((NW)) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。