- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19474 > ADSP-2105BPZ-80 (Analog Devices Inc)IC DSP CONTROLLER 16BIT 68PLCC PDF資料下載

參數(shù)資料

| 型號: | ADSP-2105BPZ-80 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 21/64頁 |

| 文件大小: | 0K |

| 描述: | IC DSP CONTROLLER 16BIT 68PLCC |

| 標準包裝: | 19 |

| 系列: | ADSP-21xx |

| 類型: | 定點 |

| 接口: | 同步串行端口(SSP) |

| 時鐘速率: | 20MHz |

| 非易失內(nèi)存: | 外部 |

| 芯片上RAM: | 3kB |

| 電壓 - 輸入/輸出: | 5.00V |

| 電壓 - 核心: | 5.00V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應商設備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

| 產(chǎn)品目錄頁面: | 738 (CN2011-ZH PDF) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

ADSP-21xx

–28–

REV. B

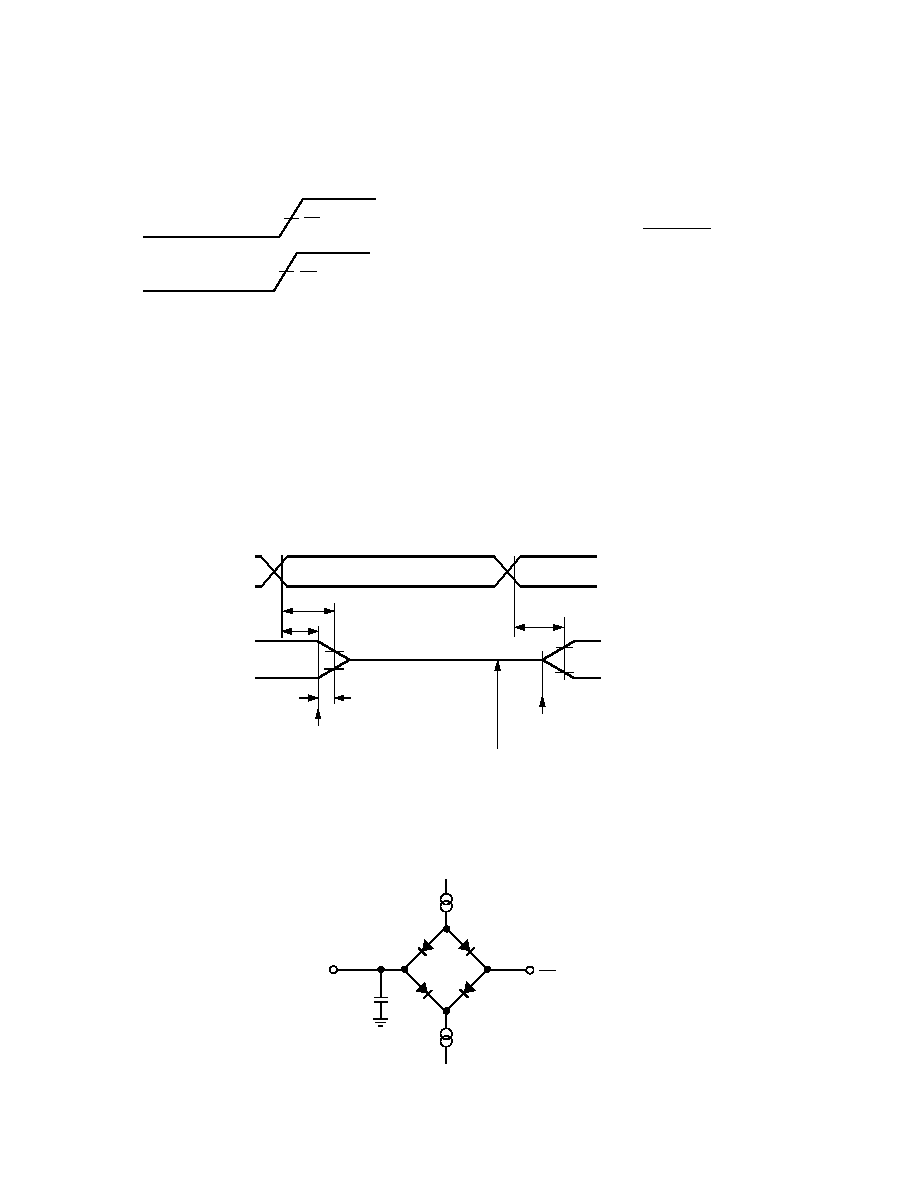

The decay time, tDECAY, is dependent on the capacitative load,

CL, and the current load, iL, on the output pin. It can be

approximated by the following equation:

t

DECAY =

C

L × 0.5 V

i

L

from which

tDIS = tMEASURED – tDECAY

is calculated. If multiple pins (such as the data bus) are dis-

abled, the measurement value is that of the last pin to stop

driving.

Output Enable Time

Output pins are considered to be enabled when they have made

a transition from a high-impedance state to when they start

driving. The output enable time (t ENA) is the interval from

when a reference signal reaches a high or low voltage level to

when the output has reached a specified high or low trip point,

as shown in Figure 27. If multiple pins (such as the data bus)

are enabled, the measurement value is that of the first pin to

start driving.

SPECIFICATIONS (ADSP-2103/2162/2164)

TEST CONDITIONS

Figure 26 shows voltage reference levels for ac measurements.

Figure 26. Voltage Reference Levels for AC Measurements

(Except Output Enable/Disable)

Output Disable Time

Output pins are considered to be disabled when they have

stopped driving and started a transition from the measured

output high or low voltage to a high impedance state. The

output disable time (tDIS) is the difference of tMEASURED and

tDECAY, as shown in Figure 27. The time tMEASURED is the

interval from when a reference signal reaches a high or low

voltage level to when the output voltages have changed by 0.5 V

from the measured output high or low voltage.

INPUT

OUTPUT

VDD

2

VDD

2

2.0V

1.0V

t

ENA

REFERENCE

SIGNAL

OUTPUT

t

DECAY

VOH (MEASURED)

OUTPUT STOPS

DRIVING

OUTPUT STARTS

DRIVING

t

DIS

t

MEASURED

VOL (MEASURED)

VOH (MEASURED) – 0.5V

VOL (MEASURED) +0.5V

HIGH-IMPEDANCE STATE.

TEST CONDITIONS CAUSE

THIS VOLTAGE LEVEL TO BE

APPROXIMATELY 1.5V.

VOH (MEASURED)

VOL (MEASURED)

TO

OUTPUT

PIN

50pF

IOH

IOL

VDD

2

Figure 27. Output Enable/Disable

Figure 28. Equivalent Device Loading for AC Measurements

(Except Output Enable/Disable)

相關PDF資料 |

PDF描述 |

|---|---|

| EEM06DTMH | CONN EDGECARD 12POS R/A .156 SLD |

| HSC40DRTF-S13 | CONN EDGECARD 80POS .100 EXTEND |

| XC95288XL-7FG256C | IC CPLD 288 MCELL C-TEMP 256FBGA |

| VI-B7L-CX-B1 | CONVERTER MOD DC/DC 28V 75W |

| TAP336J010CRW | CAP TANT 33UF 10V 5% RADIAL |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2105BPZ-80 | 制造商:Analog Devices 功能描述:IC 16-BIT MICROCOMPUTER |

| ADSP-2105BPZ-80RL | 制造商:Analog Devices 功能描述: |

| ADSP-2105KP-40 | 制造商:Analog Devices 功能描述:Digital Signal Processor, 16 Bit, 68 Pin, Plastic, PLCC |

| ADSP2105KP55 | 制造商:AD 功能描述:* |

| ADSP-2105KP-55 | 制造商:Analog Devices 功能描述:SEMICONDUCTOR ((NW)) |

發(fā)布緊急采購,3分鐘左右您將得到回復。