- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19463 > ADSP-21065LKSZ-264 (Analog Devices Inc)IC DSP CONTROLL 544KBIT 208-MQFP PDF資料下載

參數(shù)資料

| 型號: | ADSP-21065LKSZ-264 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 9/44頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DSP CONTROLL 544KBIT 208-MQFP |

| 產(chǎn)品培訓(xùn)模塊: | SHARC Processor Overview |

| 標準包裝: | 1 |

| 系列: | SHARC® |

| 類型: | 浮點 |

| 接口: | 主機接口,串行端口 |

| 時鐘速率: | 60MHz |

| 非易失內(nèi)存: | 外部 |

| 芯片上RAM: | 64kB |

| 電壓 - 輸入/輸出: | 3.30V |

| 電壓 - 核心: | 3.30V |

| 工作溫度: | 0°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-MQFP(28x28) |

| 包裝: | 托盤 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

REV. C

ADSP-21065L

–17–

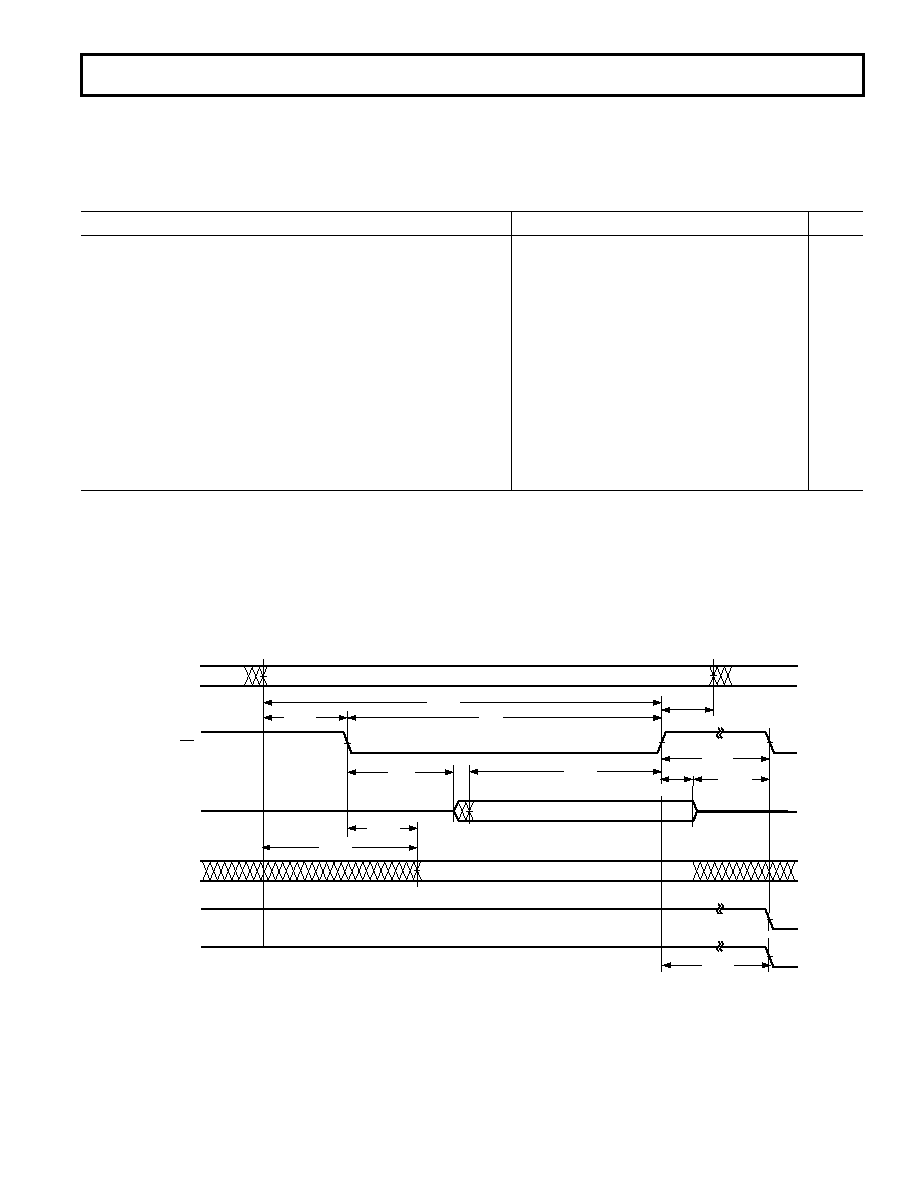

Memory Write—Bus Master

Use these specifications for asynchronous interfacing to memories (and memory-mapped peripherals) without reference to CLKIN.

These specifications apply when the ADSP-21065L is the bus master when accessing external memory space. These switching

characteristics also apply for bus master synchronous read/write timing (see Synchronous Read/Write—Bus Master below). If these

timing requirements are met, the synchronous read/write timing can be ignored (and vice versa). An exception to this is the ACK pin

timing requirements as described in the note below.

Parameter

Min

Max

Unit

Timing Requirements:

tDAAK

ACK Delay from Address

1, 2

24.0 + 30 DT + W

ns

tDSAK

ACK Delay from

WR Low1

19.5 + 24 DT + W

ns

Switching Characteristics:

tDAWH

Address, Selects to

WR Deasserted2

29.0 + 31 DT + W

ns

tDAWL

Address, Selects to

WR Low2

3.5 + 6 DT

ns

tWW

WR Pulsewidth

24.5 + 25 DT + W

ns

tDDWH

Data Setup Before

WR High

15.5 + 19 DT + W

ns

tDWHA

Address Hold After

WR Deasserted

0.0 + 1 DT + H

ns

tDATRWH

Data Disable After

WR Deasserted3

1.0 + 1 DT + H

4.0 + 1 DT + H

ns

tWWR

WR High to WR, RD Low

4.5 + 7 DT + H

ns

tWRDGL

WR High to DMAGx Low

11.0 + 13 DT + H

ns

tDDWR

Data Disable Before

WR or RD Low

3.5 + 6 DT + I

ns

tWDE

WR Low to Data Enabled

4.5 + 6 DT

ns

W = (number of wait states specified in WAIT register)

tCK.

H = tCK (if an address hold cycle occurs, as specified in WAIT register; otherwise H = 0).

I = tCK (if a bus idle cycle occurs, as specified in WAIT register; otherwise I = 0).

NOTES

1ACK is not sampled on external memory accesses that use the Internal wait state mode. For the first CLKIN cycle of a new external memory access, ACK must be

valid by tDAAK or tDSAK or synchronous specification tSACKC for wait state modes External, Either, or Both (Both, if the internal wait state is zero). For the second and

subsequent cycles of a wait stated external memory access, synchronous specifications t SACKC and tHACKC must be met for wait state modes External, Either, or Both

(Both, after internal wait states have completed).

2The falling edge of

MSx, SW, and BMS is referenced.

3See System Hold Time Calculation under Test Conditions for calculation of hold times given capacitive and dc loads.

RD

ACK

DATA

WR

ADDRESS

MSx , SW

BMS

tDAWL

tWW

tDAAK

tWWR

tWDE

tDDWR

tDWHA

tDDWH

tDAWH

tDSAK

DMAG

tDATRWH

tWRDGL

Figure 12. Memory Write—Bus Master

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GEC06DRES-S13 | CONN EDGECARD 12POS .100 EXTEND |

| 180-015-102L001 | CONN DB15 MALE HD SOLDER CUP TIN |

| 171-025-203L031 | CONN DB25 FEMALE SLD CUP NICKEL |

| AGM24DTBN-S189 | CONN EDGECARD 48POS R/A .156 SLD |

| AYM24DTBH-S189 | CONN EDGECARD 48POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2106X | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer Family |

| ADSP-2109 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Cost DSP Microcomputers |

| ADSP-2109KP-80 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Cost DSP Microcomputers |

| ADSP-2109LKP-55 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Low Cost DSP Microcomputers |

| ADSP-2111 | 制造商:AD 制造商全稱:Analog Devices 功能描述:ADSP-2100 Family DSP Microcomputers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。