- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376804 > DM9601E (Electronic Theatre Controls, Inc.) USB Ethernet MAC Controller with Intergrated 10/100 PHY PDF資料下載

參數(shù)資料

| 型號: | DM9601E |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | USB Ethernet MAC Controller with Intergrated 10/100 PHY |

| 中文描述: | USB以太網(wǎng)MAC控制器與集成10/100網(wǎng)卡芯片 |

| 文件頁數(shù): | 19/58頁 |

| 文件大小: | 603K |

| 代理商: | DM9601E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

DM9601

USB to Ethernet MAC Controller with Integrated 10/100 PHY

Final

Version: DM9601-DS-F01

June 22, 2002

19

Key to Default

In the register description that follows, the default column

takes the form:

<Reset Value>, <Access Type>

Where

:

<Reset Value>:

1

Bit set to logic one

0

Bit set to logic zero

X

No default value

<Access Type>:

RO = Read only

RW = Read/Write

R/C = Read

and Clear

RW/C1=Read/Write and Cleared by write 1

WO = Write only

Reserved bits are shaded and should be written with 0.

Reserved bits are undefined on read access.

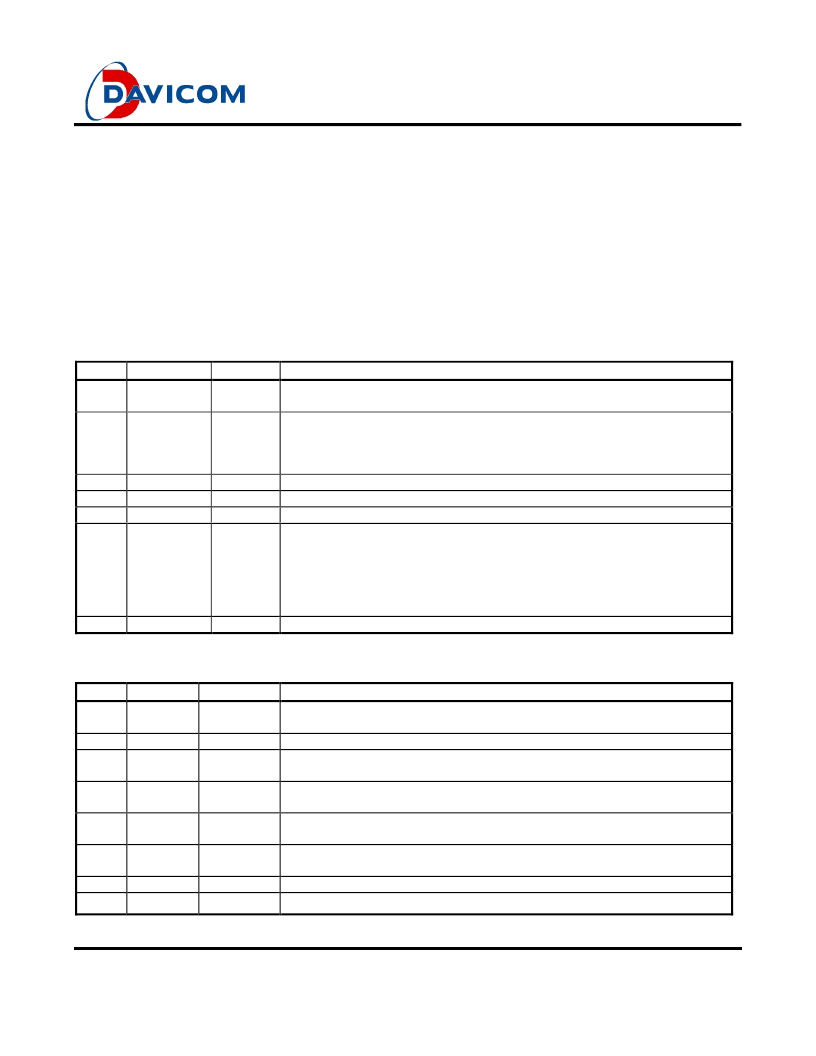

10.1 Network Control Register (00H)

Bit

7

Name

EXT_PHY

Default

0,RW

Description

Select External PHY When Set

When clear select Internal PHY. This bit will not be affected after a software reset

Wakeup Event Enable

When set, it enables the wakeup function. Clearing this bit will also clear all wakeup

event status.

This bit will not be affected after a software reset.

Reserved

Force Collision Mode, used for testing.

Full-Duplex Mode. Read only on Internal PHY mode. R/W on External PHY mode

Loopback Mode

Bit 2 1

0 0 normal

0 1 MAC internal loopback

1 0 internal PHY digital loopback

1 1 internal PHY analog loopback

Software reset and auto clear after 10us

6

WAKEEN

0,RW

5

4

3

RESERVED

FCOL

FDX

LBK

0,RO

0,RW

0,RW

00,RW

2:1

0

RST

0,RW

10.2 Network Status Register (01H)

Bit

7

Name

SPEED

Default

X,RO

Description

Media speed 0:100Mbps 1:10Mbps, when internal PHY is used. This bit is no

meaning when LINKST=0

Link status 0:link failed 1:link OK, when internal PHY is used

Wakeup Event Status

Clears by read or write 1. This bit will not be affected after a software reset

TX FIFO Full

When there are two packets in TX SRAM, TX FIFO FULL will be set

TX Packet 2 Complete Status

Clears by read or write 1.Transmit completion of packet index 2

TX Packet 1 Complete Status

Clears by read or write 1. Transmit completion of packet index 1

RX FIFO Overflow

RX Packet Ready, there are one or more packets in RX FIFO

6

5

LINKST

WAKEST

X,RO

0,RW/C1

4

TXFULL

0,RO

3

TX2END

0,RW/C1

2

TX1END

0,RW/C1

1

0

RXOV

RXRDY

0,RO

0,RO

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9602 | Dual Retriggerable, Resettable One Shots |

| DM9602N | Dual Retriggerable, Resettable One Shots |

| DM96L02 | Dual Retriggerable Resettable Monostable Multivibrator |

| DM96L02N | Dual Retriggerable Resettable Monostable Multivibrator |

| DM9701F | Gigabit Ethernet PHY Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9601J | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Retriggerable One Shot |

| DM9601N | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DM9601W | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Retriggerable One Shot |

| DM9601W/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DM9602 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Dual Retriggerable, Resettable One Shots |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。