- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376804 > DM9601E (Electronic Theatre Controls, Inc.) USB Ethernet MAC Controller with Intergrated 10/100 PHY PDF資料下載

參數(shù)資料

| 型號(hào): | DM9601E |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | USB Ethernet MAC Controller with Intergrated 10/100 PHY |

| 中文描述: | USB以太網(wǎng)MAC控制器與集成10/100網(wǎng)卡芯片 |

| 文件頁(yè)數(shù): | 25/58頁(yè) |

| 文件大小: | 603K |

| 代理商: | DM9601E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

DM9601

USB to Ethernet MAC Controller with Integrated 10/100 PHY

Final

Version: DM9601-DS-F01

June 22, 2002

25

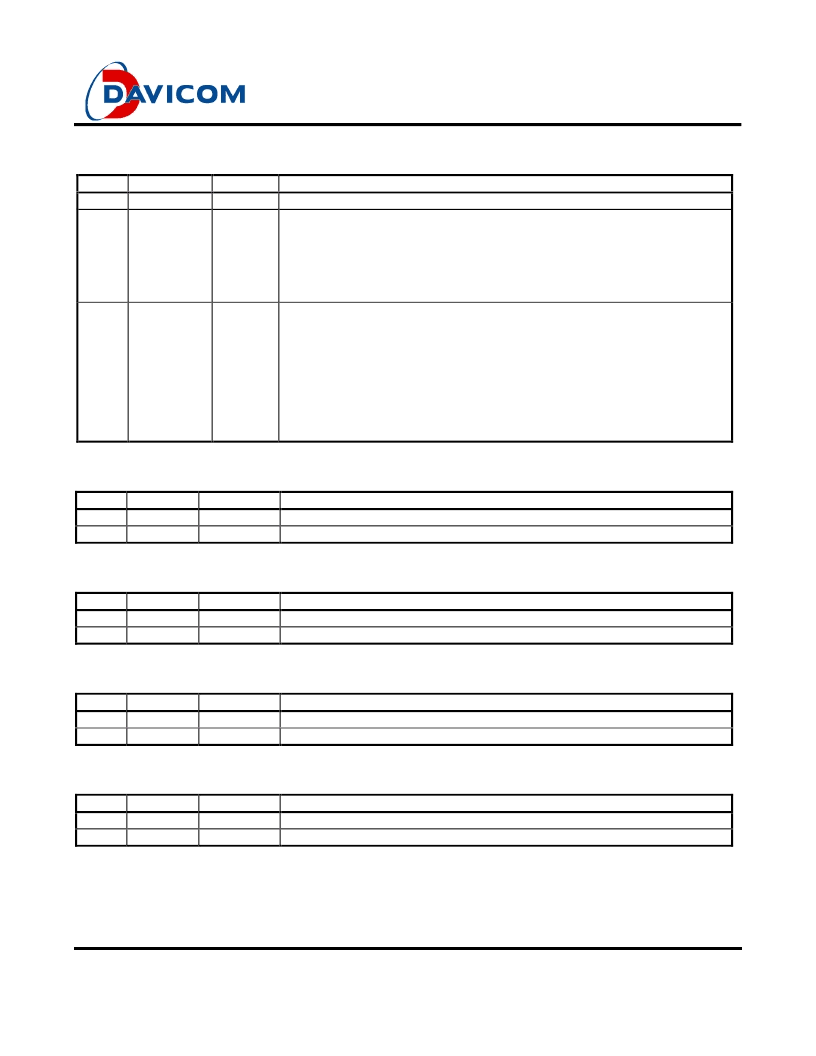

10.19 General purpose Register ( 1FH )

Bit

7

6:1

Name

RESERVED

GEPIO6-1

Default

0,RO

0,RW

Description

Reserved

General Purpose

When the correspondent bit of General Purpose Control Register is 1, the value of

the bit is output to pin GEPIO6-1

When the correspondent bit of General Purpose Control Register is 0, the value of

the bit be read is reflected from correspondent pins of GEPIIO6-1

The GEPIOs are mapped to pins GEPIO6 to GEPIO1 respectively

General Purpose

When the correspondent bit of General Purpose Control Register is 1, the value of

the bit is output to pin GEPIO0

When the correspondent bit of General Purpose Control Register is 0, the value of

the bit be read is reflected from pin GEPIO0

GEPIO0 default output 1 to POWER_DOWN internal PHY. Driver need to clear this

POWER_DOWN signal by write “0” when it wants PHY active. If other device need,

it also can refer this signal. This default value can be programmed by EEPROM.

Please refer EEPROM description

0

GEPIO0

1,RW

10.20 TX SRAM Write Pointer Address Register (20H~21H)

Bit

7:0

7:0

Name

TWPAH

TWPAL

Default

00H,RO

00H.RO

Description

TX SRAM write pointer address high byte (21H)

TX SRAM write pointer address low byte (20H)

10.21 TX SRAM Read Pointer Address Register (22H~23H)

Bit

7:0

7:0

Name

TRPAH

TRPAL

Default

00H,RO

00H.RO

Description

TX SRAM read pointer address high byte (23H)

TX SRAM read pointer address low byte (22H)

10.22 RX SRAM Write Pointer Address Register (24H~25H)

Bit

7:0

7:0

Name

RWPAH

RWPAL

Default

0CH,RO

04H.RO

Description

RX SRAM write pointer address high byte (25H)

RX SRAM write pointer address low byte (24H)

10.23 RX SRAM Read Pointer Address Register (26H~27H)

Bit

7:0

7:0

Name

RRPAH

RRPAL

Default

0CH,RO

00H.RO

Description

RX SRAM read pointer address high byte (27H)

RX SRAM read pointer address low byte (26H)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9602 | Dual Retriggerable, Resettable One Shots |

| DM9602N | Dual Retriggerable, Resettable One Shots |

| DM96L02 | Dual Retriggerable Resettable Monostable Multivibrator |

| DM96L02N | Dual Retriggerable Resettable Monostable Multivibrator |

| DM9701F | Gigabit Ethernet PHY Transceiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9601J | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Retriggerable One Shot |

| DM9601N | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DM9601W | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Retriggerable One Shot |

| DM9601W/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| DM9602 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Dual Retriggerable, Resettable One Shots |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。