- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375864 > FMS7401 (Fairchild Semiconductor Corporation) Digital Power Controller PDF資料下載

參數(shù)資料

| 型號: | FMS7401 |

| 廠商: | Fairchild Semiconductor Corporation |

| 元件分類: | 基準(zhǔn)電壓源/電流源 |

| 英文描述: | Digital Power Controller |

| 中文描述: | 數(shù)字電源控制器 |

| 文件頁數(shù): | 19/80頁 |

| 文件大小: | 1535K |

| 代理商: | FMS7401 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

PRODUCT SPECIFICATION

FMS7401/7401L

REV. 1.0.2 6/23/04

19

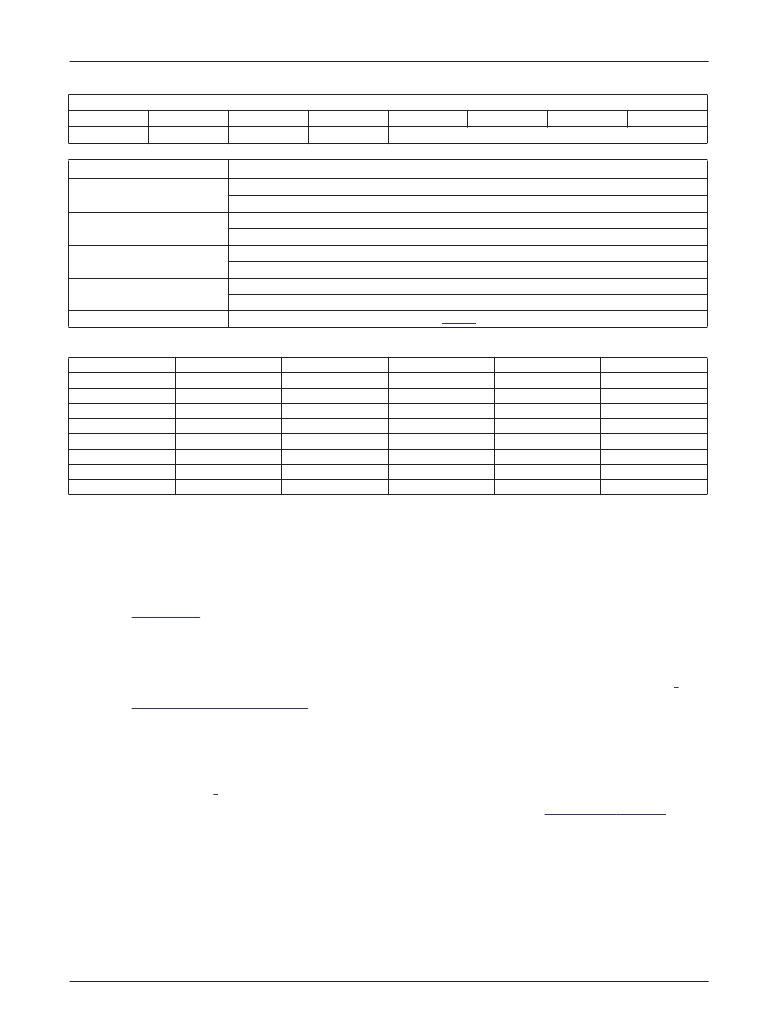

Table 5. ADCNTRL1 Register Bit Definitions

Table 6. Analog Input Channel Selection (ACHSEL[3:0]) Bit Definitions

ACHSEL[3]

ACHSEL[2]

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

1

4.1.2 ADCNTRL2 Register

The ADCNTRL2 is an 8-bit memory map register used to configure the analog circuits. Six of the eight register bits are used to

configure circuits directly related to the ADC circuit while the others are not related.

Bit 7 (REFBY2) of the ADCNTRL2 register is the reference clock (F

RCLK1

) divide-by-2 enable bit. The REFBY2 bit config-

ures the reference clock of the PLL and Programmable Comparator circuit to be sourced either by F

RCLK1

or F

RCLK1

/2 clock.

Refer to the

Clock Circuit

section of the datasheet for additional details.

Bit 6 (COMPSEL) of the ADCNTRL2 register is the Programmable Comparator’s non-inverting input selection bit. If

COMPSEL=0, the non-inverting input of the Programmable Comparator is the G4/AIN0 device pin. If COMPSEL=1, the

non-inverting input of the Programmable Comparator is the G2/AIN2 device pin. Before enabling the Programmable

Comparator circuit, the selected analog input port pin must be configured as a tri-state input bypassing the I/O circuitry.

9

Refer to the

Programmable Comparator Circuit

section of the datasheet for addition details.

Bit 5 of the ADCNTRL2 register is the Uncommitted Amplifier Enable (ENAMP) bit. If ENAMP=0, the Uncommitted Ampli-

fier circuit is disabled and its pin connections (G6/-A

IN

and G7/A

OUT

) may be used as normal I/O ports. The G7/AIN4 pin may

still be used as a standard ADC conversion input through the analog ACH5 channel. If ENAMP=1, the Uncommitted Amplifier

circuit is enabled and its pin connections must be configured as tri-state inputs where G6/-A

IN

is the inverting input and G7/

A

OUT

is the amplifier output.

9

If the ADC circuit is performing a conversion on the analog ACH5 input when driven by the

Uncommitted Amplifier, software must avoid clearing the ENAMP bit. Refer to the following

Uncommitted Amplifier

section

for additional details.

Bit 4 (ENDAS) of the ADCNTRL2 register enables the ADC conversion’s gated auto-sampling operating mode. If ENDAS=1,

the ADC circuit configures the F

ADCLK

clock for synchronization with the PWM Timer 1’s ADSTROBE output signal. The

ADC circuit will then accept triggers by the active (on) edge transition of the ADSTROBE signal. All other ADC configuration

ADCNTRL1 Register (addr. 0x9F)

Bit 4

REFSEL

Bit 7

APND

Bit 6

AINTEN

Bit 5

ASTART

Bit 3

Bit 2

Bit 1

Bit 0

ACHSEL[3:0]

APND

Description

(0) ADC’s pending flag is cleared.

(1) ADC’s pending flag is triggered.

(0) Disables ADC hardware interrupts.

(1) Enables ADC hardware interrupts.

(0) ADC conversion is not in progress.

(1) Start an ADC conversion / ADC conversion in progress.

(0) ADC Reference (V

AREF

) = Internal V

REF

(1) ADC Reference (V

AREF

) = Vcc

Analog Input Channel Selection Bits. Refer to

Table 6

for details.

AINTEN

ASTART

REFSEL

ACHSEL[3:0]

ACHSEL[1]

0

0

1

1

0

0

1

0

ACHSEL[0]

0

1

0

1

0

1

0

0

Analog Channel

ACH1

ACH2

ACH3

ACH4

ACH5

AGND

+V

REF

Vcc/3

I/O Equiv.

G4/AIN0

G3/AIN1

G2/AIN2

G1/AIN3

G7/AIN4/A

OUT

-

-

-

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMS7401LEN | Digital Power Controller |

| FMS7401LEN14 | Digital Power Controller |

| FMS7401LVN | Digital Power Controller |

| FMS7401LVN14 | Digital Power Controller |

| FMS7G10US60S | SWTCH ROLLER SPDT 20A SCRW TERM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMS7401L | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

| FMS7401L_05 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

| FMS7401LA_ABA3026U WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| FMS7401LEM8X | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

| FMS7401LEMT8X | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Digital Power Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。